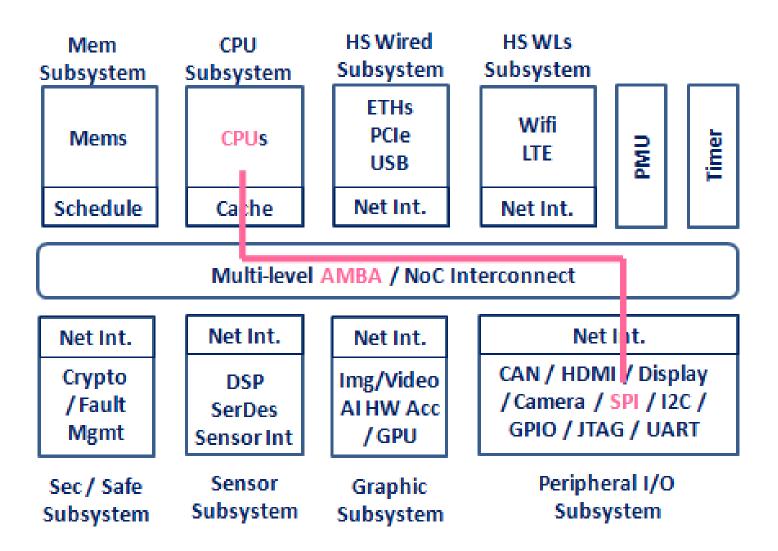

# SPI Bus (Serial Peripheral Interface Bus) SoC – SPI (for slow PCs)

Tuan Nguyen-viet

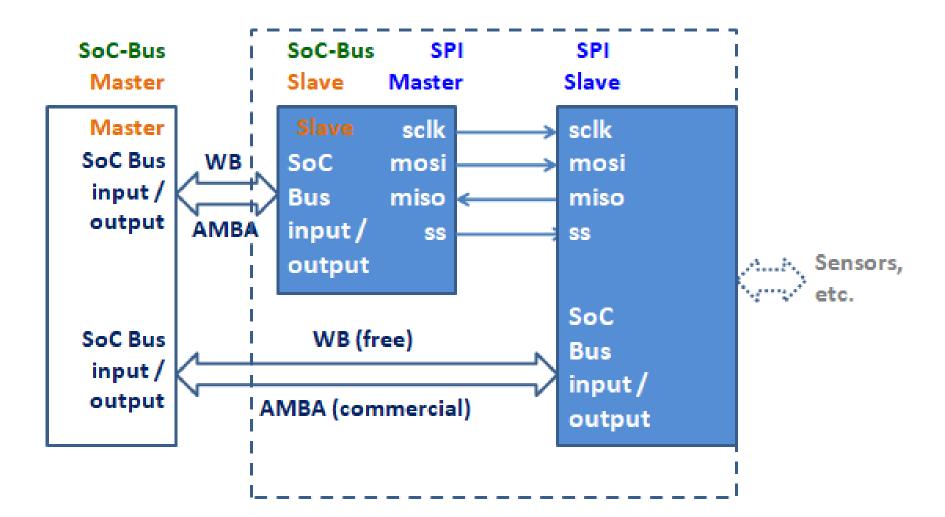

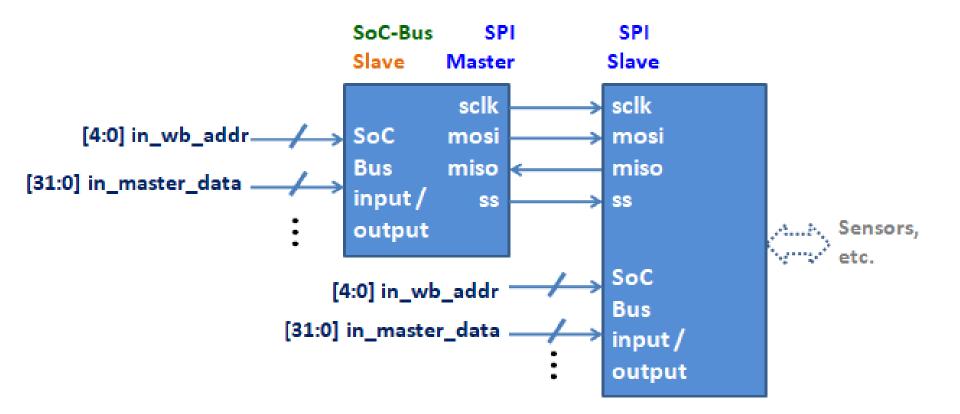

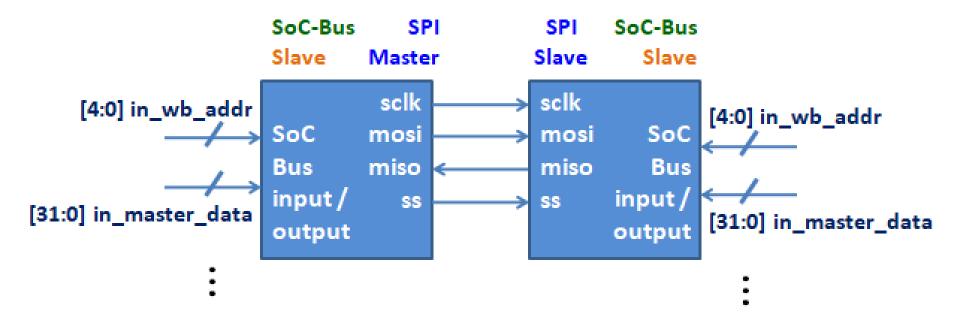

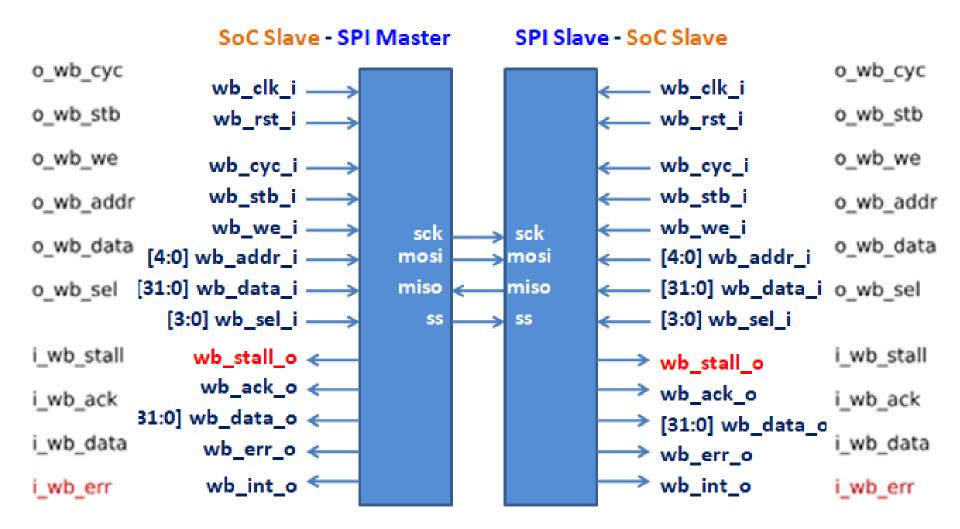

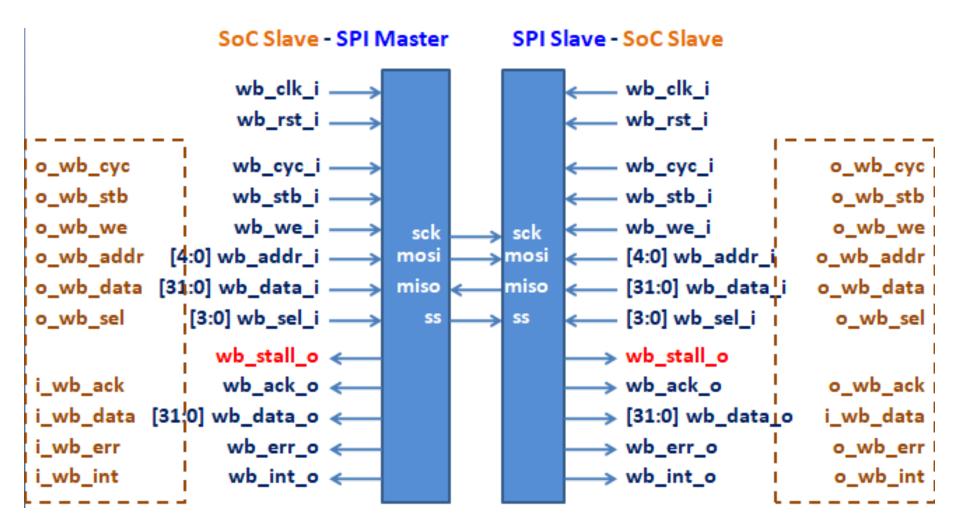

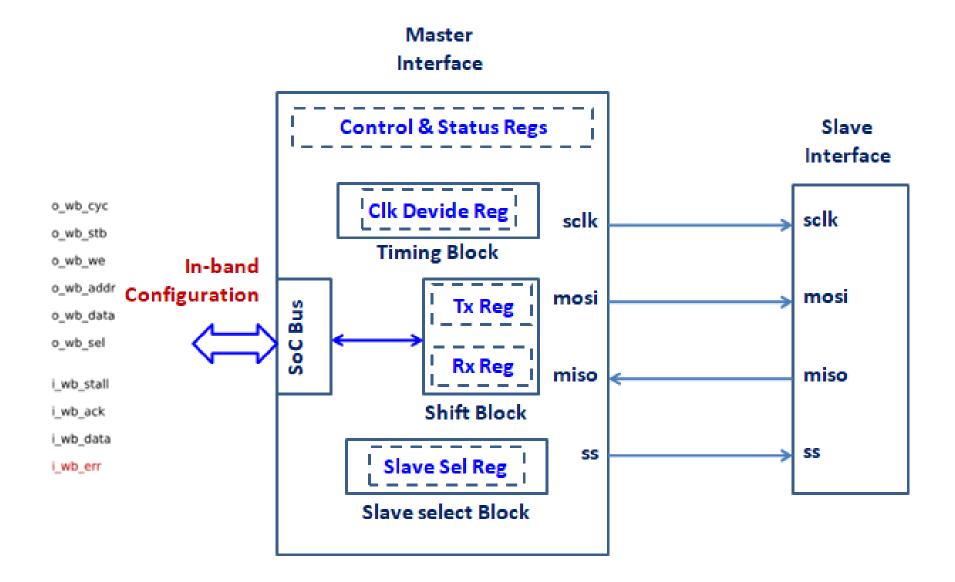

### **Processor-SPI Interaction**

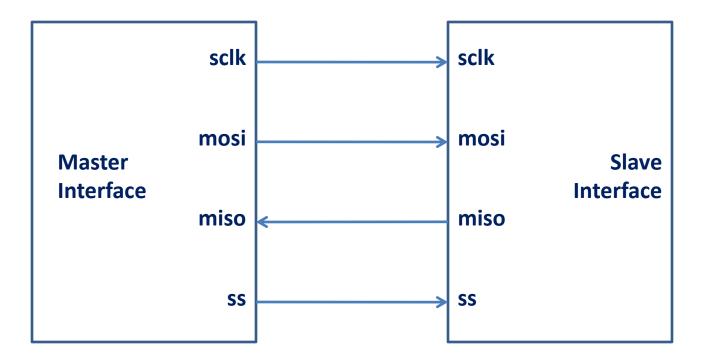

### **SPI Master / Slave**

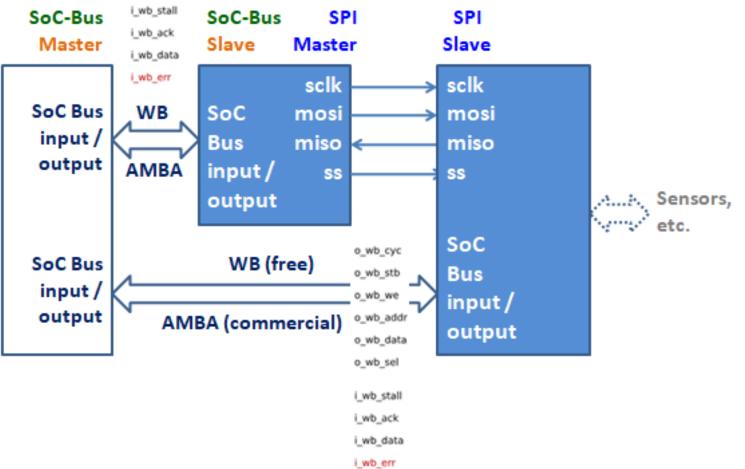

o\_wb\_stb

o\_wb\_we

o\_wb\_addr

o\_wb\_data

o\_wb\_sel

### Interface

#### **SPI Phases**

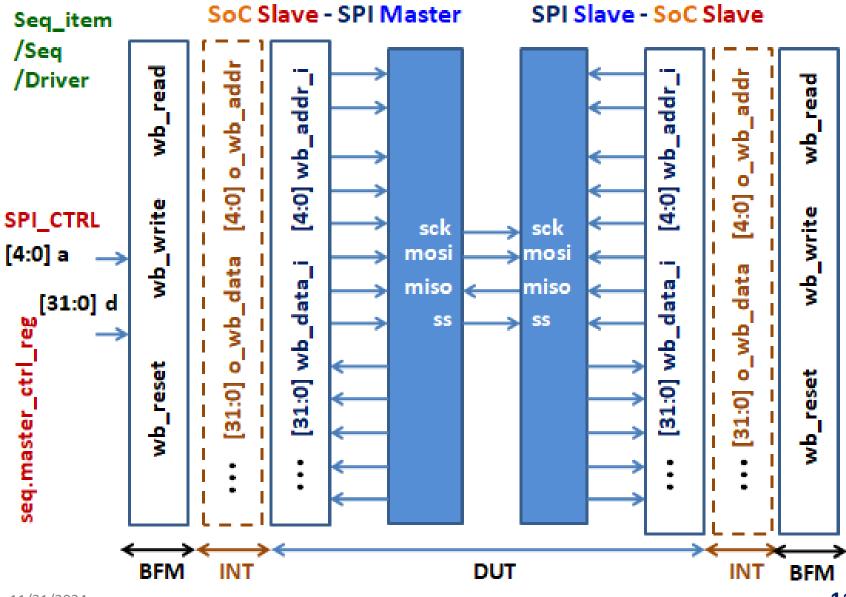

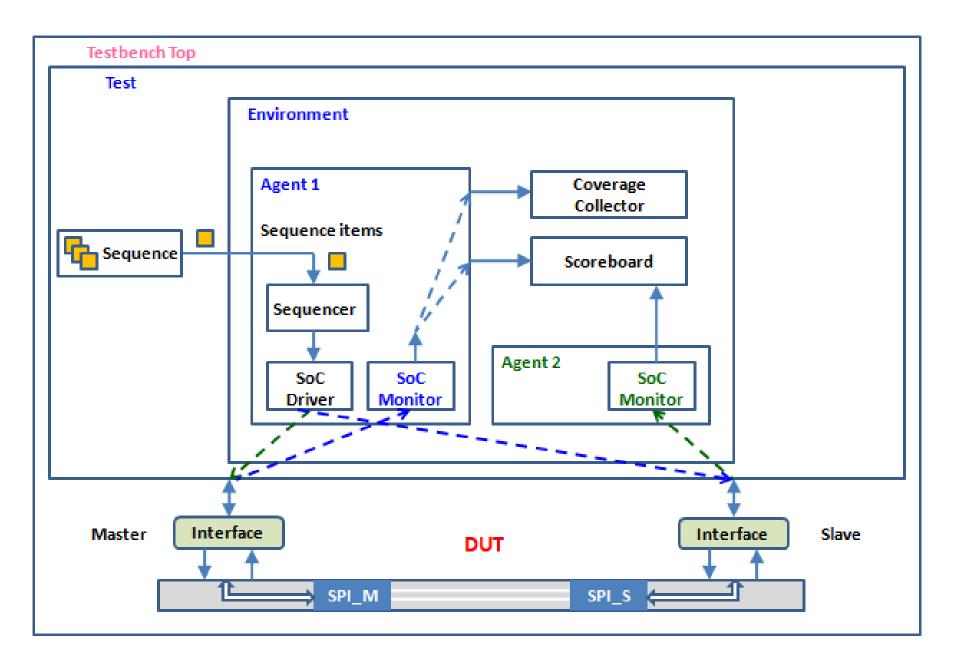

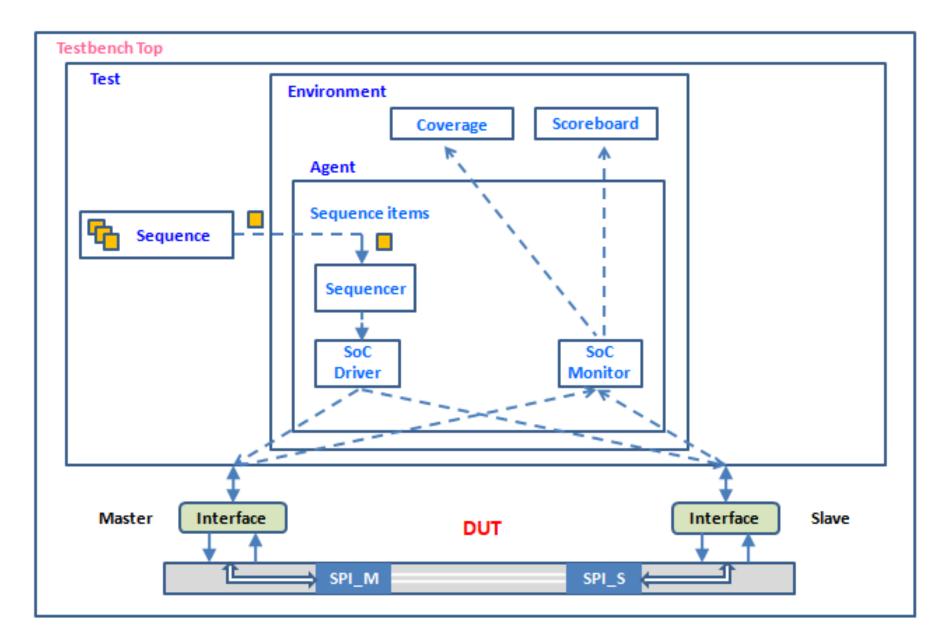

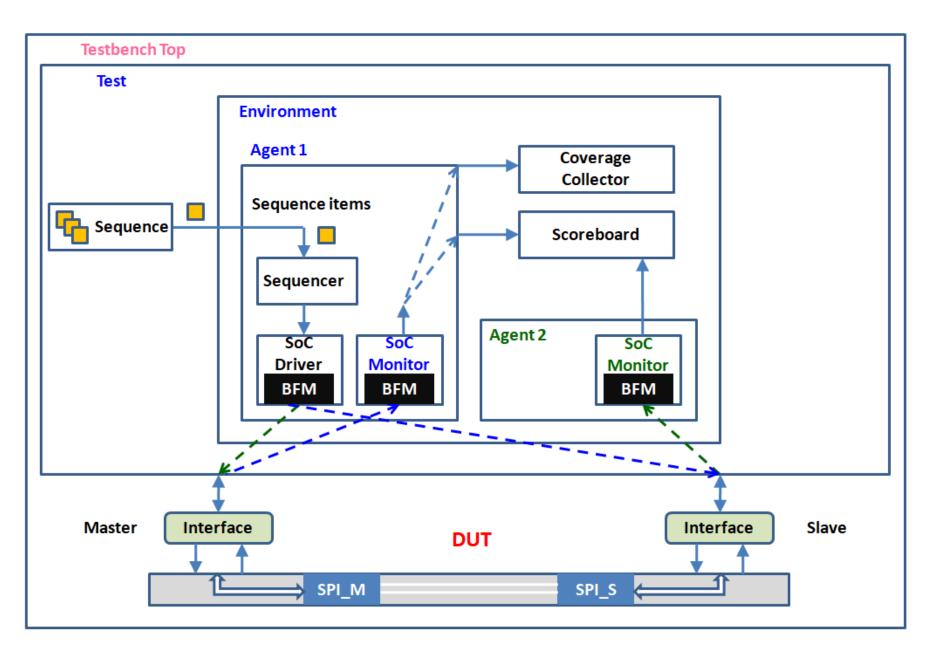

# **SoC BFM/Interface/DUT**

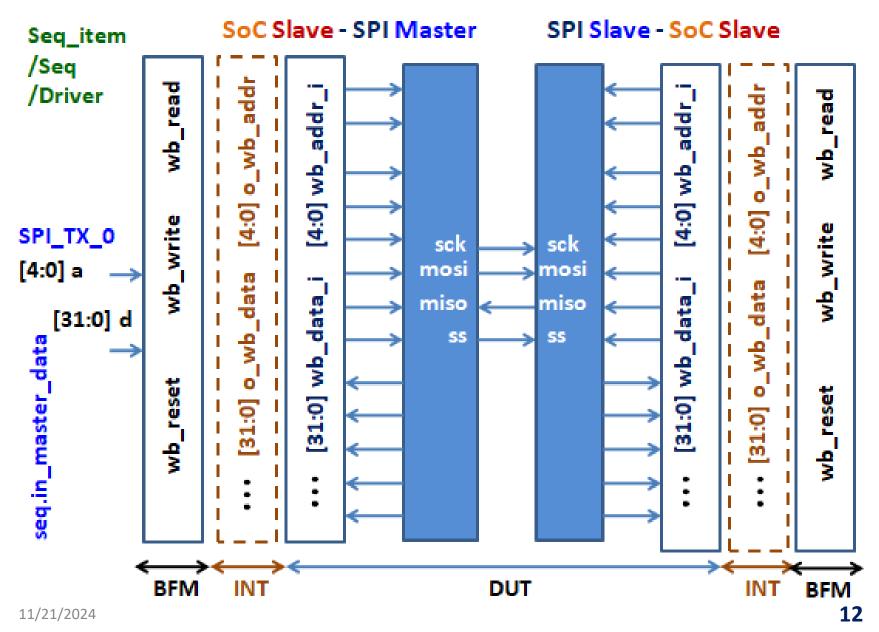

# **SoC BFM/Interface/DUT**

11/21/2024

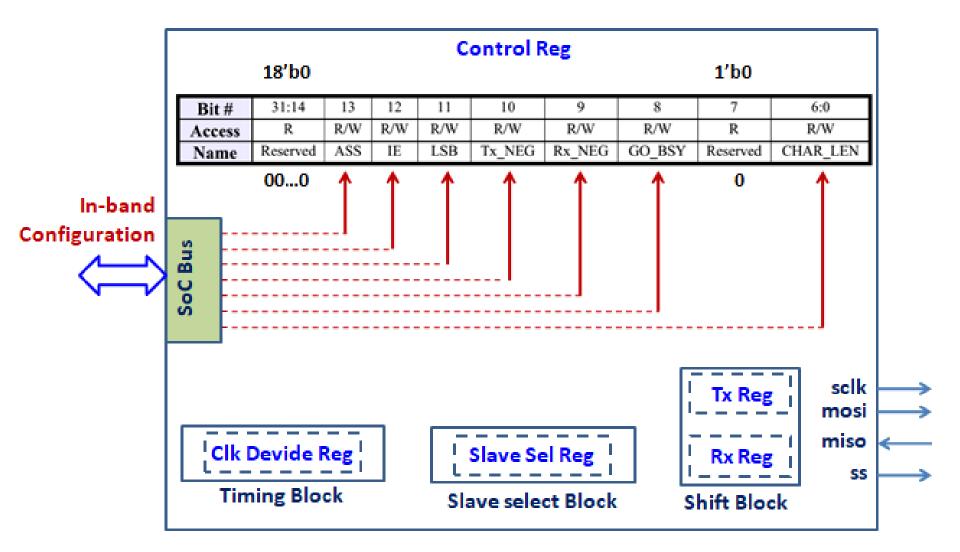

## **SPI Registers**

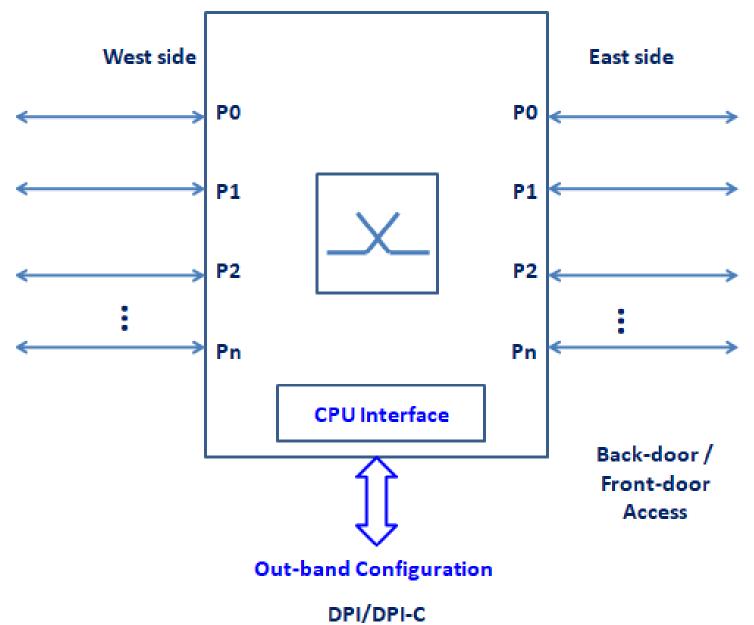

#### Packet Switch / SDN Switch

#### **SPI Master Interface**

## **SoC Bus (Slave) of SPI Master Interface**

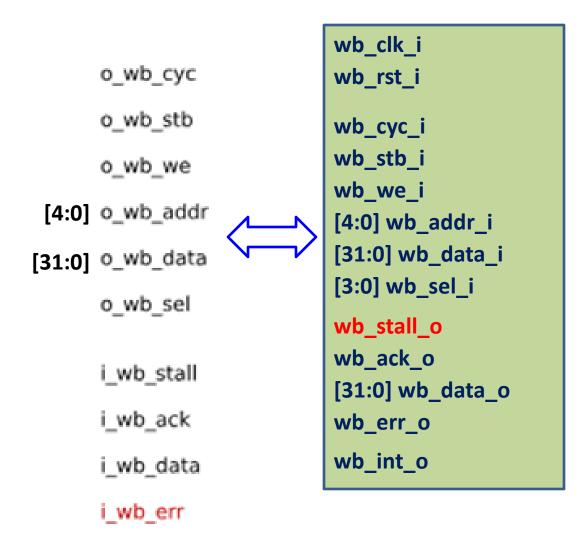

# **DUT – SoC WB Bus Interface**

| Port     | Width | Direction | Description                     |  |

|----------|-------|-----------|---------------------------------|--|

| wb_clk_i | 1     | Input     | Master clock                    |  |

| wb_rst_i | 1     | Input     | Synchronous reset, active high  |  |

| wb_adr_i | 5     | Input     | Lower address bits              |  |

| wb_dat_i | 32    | Input     | Data towards the core           |  |

| wb_dat_o | 32    | Output    | Data from the core              |  |

| wb_sel_i | 4     | Input     | Byte select signals             |  |

| wb_we_i  | 1     | Input     | Write enable input              |  |

| wb_stb_i | 1     | Input     | Strobe signal/Core select input |  |

| wb_cyc_i | 1     | Input     | Valid bus cycle input           |  |

| wb_ack_o | 1     | Output    | Bus cycle acknowledge output    |  |

| wb_err_o | 1     | Output    | Bus cycle error output          |  |

| wb_int_o | 1     | Output    | Interrupt signal output         |  |

- May use a typical at: <u>https://opencores.org/projects/spi</u>

- And <u>https://github.com/xfguo/spi/tree/master/rtl/verilog</u>

- And

https://opencores.org/websvn/filedetails?repname=spi&path=%2Fspi%2F trunk%2Fdoc%2Fspi.pdf

| Reg<br>Name | Access<br>Address | Bus Width | Access Mode | Description                 |

|-------------|-------------------|-----------|-------------|-----------------------------|

| RxO         | 0x00              | 32        | R           | Receive data register 0     |

| Rx1         | 0x04              | 32        | R           | Receive data register 1     |

| Rx2         | 0x08              | 32        | R           | Receive data register 2     |

| Rx3         | 0x0C              | 32        | R           | Receive data register 3     |

| Tx0         | 0x00              | 32        | W/R         | Transmit data register 0    |

| Tx1         | 0x04              | 32        | W/R         | Transmit data register 1    |

| Tx2         | 0x08              | 32        | W/R         | Transmit data register 2    |

| Tx3         | 0x0C              | 32        | W/R         | Transmit data register 3    |

| CTRL        | 0x10              | 32        | W/R         | Control and Status register |

| DIVIDER     | 0x14              | 32        | W/R         | Clock dividing register     |

| SS          | 0x18              | 32        | W/R         | Slave chip select register  |

• May use a typical at: <u>https://opencores.org/projects/spi</u>

• And <u>https://github.com/xfguo/spi/tree/master/rtl/verilog</u>

### **32-bit Receive Data Reg**

• Reset Value: 0x0000000

| Bit #  | 31:0 |

|--------|------|

| Access | R    |

| Name   | Rx   |

### **32-bit Transmit Data Reg**

• Reset Value: 0x0000000

| Bit #  | 31:0 |

|--------|------|

| Access | R/W  |

| Name   | Tx   |

# **Configuration Note**

- We use **Receive data register 0** that holds the value of data received from the last transfer.

- **CTRL register** holds the data word length field:

- E.g., if use CTRL [9:3] (... 00 0000 1000) that is set to 0x10,

- Then, bits Rx[15:0] (16 low bits) can hold 16-bit received data.

- If CTRL[9:3] is set to 0x08, bit RxL[7:0] holds the received data

- We use **Transmit data register 0** that holds the value of data received from the last transfer.

- **CTRL register** holds the data word length field:

- E.g., if use CTRL [9:3] (... 00 0000 1000) that is set to 0x10,

- Then, bits Tx[15:0] (16 low bits) can hold 16-bit received data.

- if CTRL[9:3] is set

to 0x08, the bit Tx0[7:0] will be transmitted in next transfer

## **Control and Status register [CTRL]**

• Reset Value: 0x0000000

| Bit #  | 31:14    | 13  | 12  | 11  | 10     | 9      | 8      | 7        | 6:0      |

|--------|----------|-----|-----|-----|--------|--------|--------|----------|----------|

| Access | R        | R/W | R/W | R/W | R/W    | R/W    | R/W    | R        | R/W      |

| Name   | Reserved | ASS | IE  | LSB | Tx_NEG | Rx_NEG | GO_BSY | Reserved | CHAR_LEN |

# **Configuration Note (2)**

- Automatic SS (ASS) bit

- When the automatic SS bit (ASS) is set, the o\_ss signal is generated automatically.

- Data transfer is started by setting CTRL[GO\_BSY],

- the slave select (SS) signal which is selected in SS register

- is asserted by the SPI module

- and is de-asserted after the transfer is fnished.

- If ASS bit is cleared, then

- the slave select (SS) signals are asserted and de-asserted

- by writing and clearing the bits in **SS** register.

# **Configuration Note (3)**

#### IE

If this bit is set, the interrupt output is set active after a transfer is finished.

• The Interrupt signal is deasserted after a Read or Write to any register.

#### LSB

If this bit is set, the LSB is sent first on the line (bit TxL[0]), and the first bit received from the line will be put in the LSB position in the Rx register (bit RxL[0]).

• If this bit is cleared, the MSB is transmitted/received first (which bit in Tx/Rx register that is depends on the CHAR\_LEN field in the CTRL register).

# **Configuration Note (4)**

#### Tx\_NEG

If this bit is set, the **mosi** signal is changed on the falling edge of a **sclk** clock signal, or otherwise the **mosi** signal is changed on the rising edge of **sclk**.

#### Rx\_NEG

If this bit is set, the **miso** signal is latched on the falling edge of a **sclk** clock signal, or otherwise the miso signal is latched on the rising edge of **sclk**.

#### **GO\_BSY**

Writing 1 to this bit starts the transfer.

- This bit remains set during the transfer and is automatically cleared after the transfer finished.

- Writing 0 to this bit has no effect.

# **Configuration Note (5)**

NOTE:

- All registers, including the CTRL register, should be set before writing 1 to the GO\_BSY bit in the CTRL register.

- The configuration in the CTRL register must be changed with the GO\_BSY bit cleared, i.e. two Writes to the CTRL register must be executed when changing the configuration and performing the next transfer, firstly with the GO\_BSY bit cleared and secondly with GO\_BSY bit set to start the transfer.

- When a transfer is in progress, writing to any register of the SPI Master core has no effect.

# **Configuration Note (6)**

#### • CHAR\_LEN

...

This field specifies how many bits are transmitted in one transfer.

Up to 64 bits can be transmitted.

CHAR\_LEN = 0x01 ... 1 bit

CHAR\_LEN = 0x02 ... 2 bits

```

CHAR_LEN = 0x7f ... 127 bits

CHAR_LEN = 0x00 ... 128 bits

```

# **Configuration Note (6bis)**

| configuration Note (0013) | 0.45.04 64-  |

|---------------------------|--------------|

| 0x09-9 bits               | 0x15-21 bits |

| 0x0A-10 bits              | 0x16-22 bits |

| 0.00.4411                 | 0x17-23 bits |

| 0x0B-11 bits              | 0x18-24 bits |

| 0x0C-12 bits              |              |

| 0x0D-13 bits              | 0x19-25 bits |

| 0x0E-14 bits              | 0x1A-26 bits |

|                           | 0x1B-27 bits |

| 0x0F-15 bits              | 0x1C-28 bits |

| 0x10-16 bits              |              |

| 0x11-17 bits              | 0x1D-29 bits |

| 0.10.10                   | 0x1E-30 bits |

| 0x12-18 bits              | 0x1F-31 bits |

| 0x13-19 bits              | 0x20-32 bits |

|                           | 0720-22 0113 |

11/21/2024

32

0x14-20 bits

# **Clk dividing register [DIVIDER]**

• Reset Value: 0x0000ffff

| Bit #  | 31:16    | 15:0    |

|--------|----------|---------|

| Access | R        | R/W     |

| Name   | Reserved | DIVIDER |

- The value in this field is the frequency divider of the system clock **i\_wb\_clk** to generate the serial clock on the output **o\_sclk**.

- The desired frequency is obtained according to the following equation:

$$f_{sclk} = \frac{f_{wb\_clk}}{(DIVIDER+1)*2}$$

#### **SS** Reg

| Bit #  | 31:8 | 7:0 |

|--------|------|-----|

| Access | R    | R/W |

# **Configuration Note (7)**

#### • SS Register

- When CTRL[ASS] bit is cleared, writing 0x1 (0001) to any of the bit locations of this feld sets the proper o\_ss line to an active state and writing 0x0 sets the line back to the inactive state.

- When CTRL [ASS] bit is set, writing 1 to any bit location of this feld will select appropriate o\_ss line to be automatically driven to an active state for the duration of the transfer, and will be driven to an inactive state for the rest of the time.

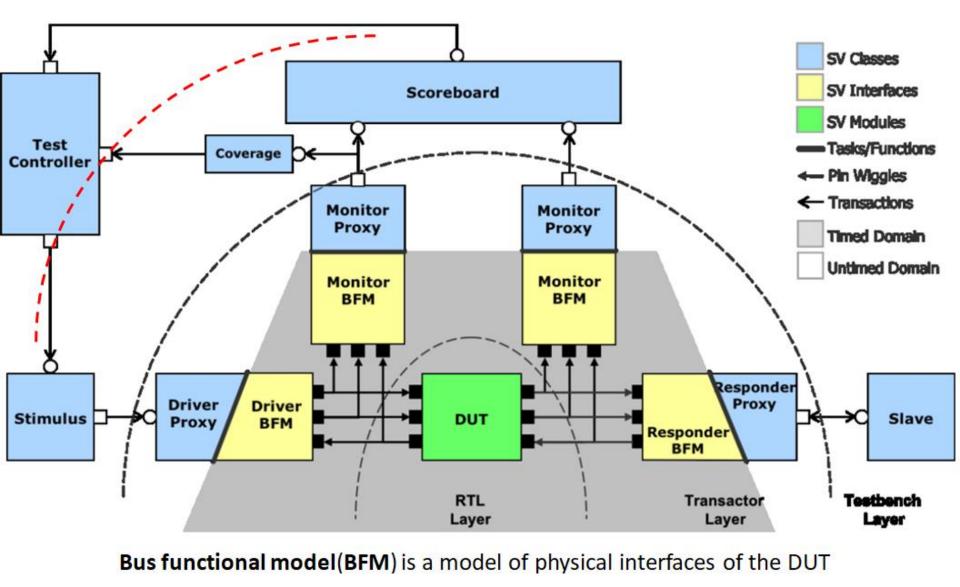

### BFM

- Bus functional model (BFM) is a model of physical interfaces of the DUT.

- It ppresents all the bus level scenario that DUT can experience on the attached bus.

- BFMs

- on one side provide the logical interface for the <u>high level</u> transactions interface to test bench components

- 2. and on another side connect to the physical interface of the DUT.

# **BFM (2)**

- Bus Functional Model (BFM) simulates **transactions/sequence items** of a bus, like READ and WRITE,

- reducing the overhead of a testbench of taking care of the timing analysis for the same.

- There are a lot more interpretations of a BFM,

- BFMs typically reduce the job of a testbench by making it more data focused.

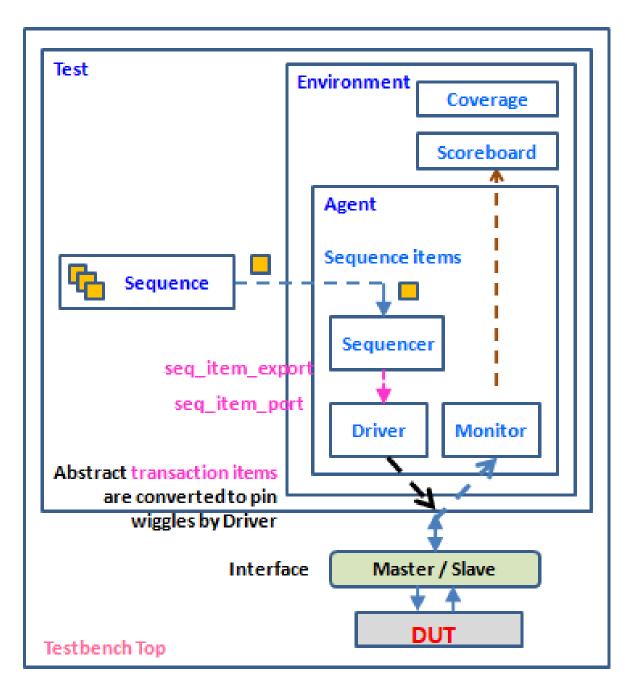

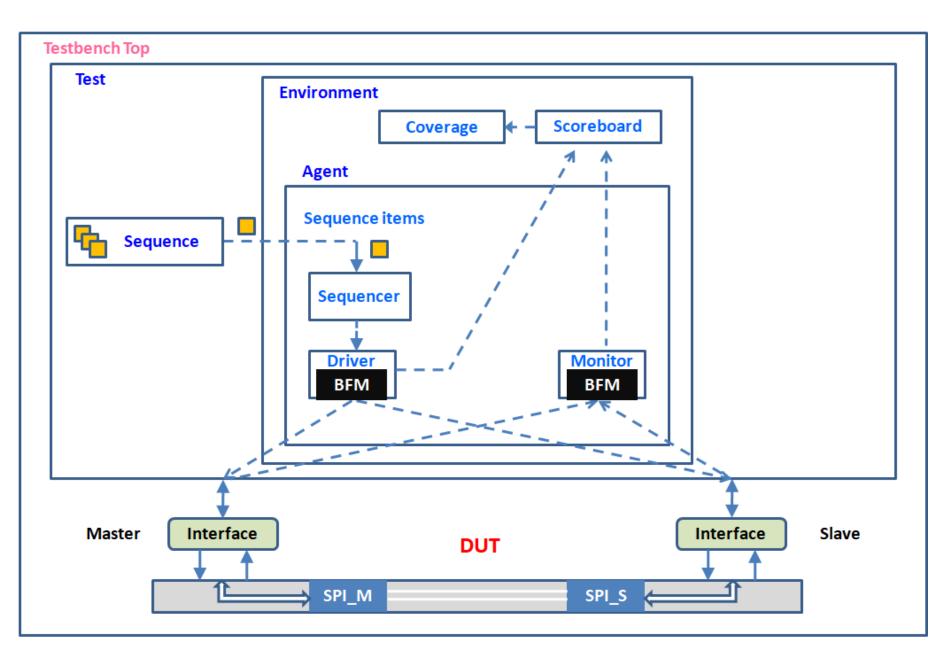

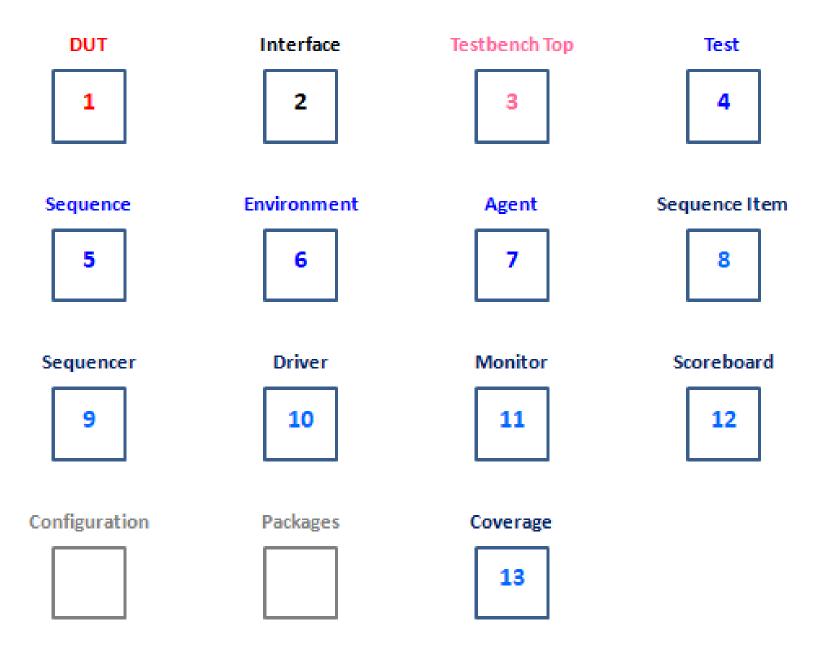

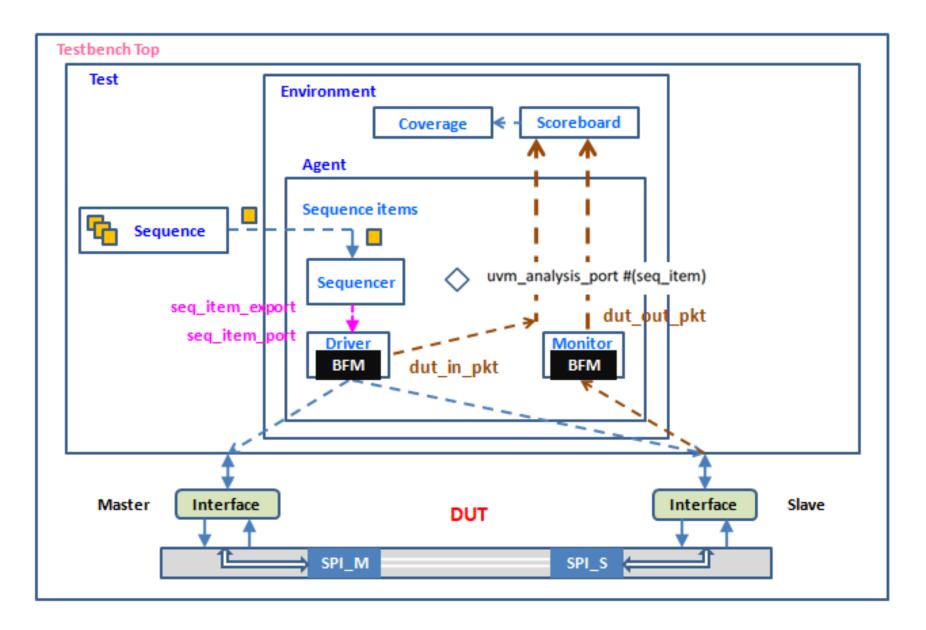

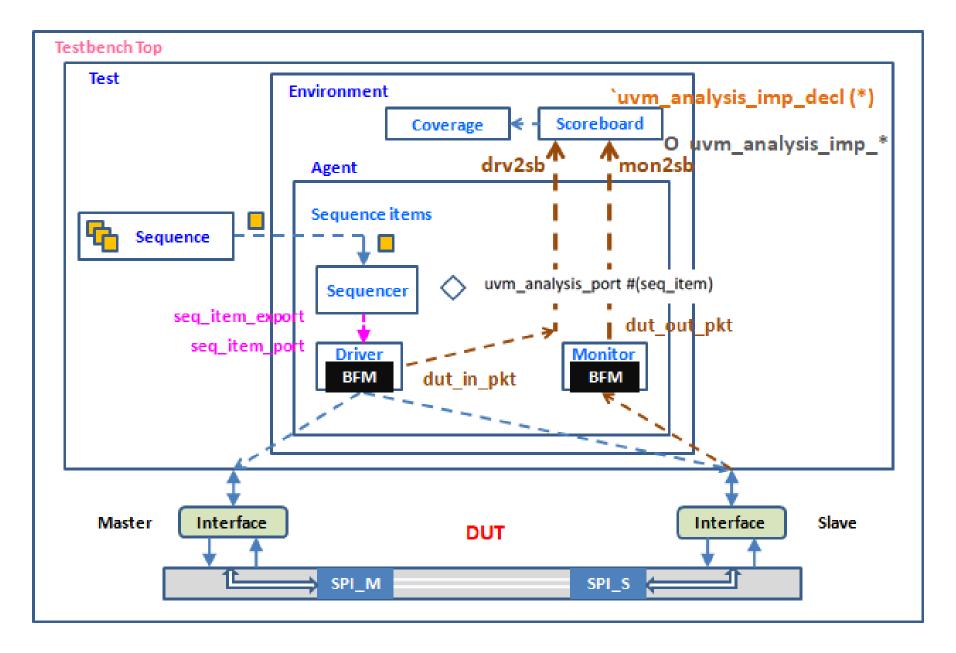

### **UVM Testbench Architecture (Cookbook)**

## Implementation

```

interface spi interface (input bit clk);

1// NOTE: interface in uvm side/domain

// SoC signals:

logic [4:0] o wb addr; // lower address bits

logic [31:0] i wb data; // data bus input

logic [31:0] o wb data; // data bus output

logic [3:0] o wb sel; // select inputs

logic o wb we; // write enable input

logic o wb stb; // strobe / core select signal

logic o_wb_cyc; // valid bus cycle input

logic i_wb_ack; // bus cycle acknowledge output

logic i_wb_err; // termination w/ error

logic i_wb_int; // interrupt request signal output input

logic tick; // transfer in complete known

clocking drive cb @(posedge clk);

input i wb data, i wb ack, i wb err, i wb int, tick;

output o wb addr, o wb data, o wb sel, o wb we, o wb stb, o wb cyc;

endclocking

clocking monitor cb @ (posedge clk);

input i wb data, i wb ack, i wb err, i wb int, tick;

output o wb addr, o wb data, o wb sel, o wb we, o wb stb, o wb cyc;

endclocking

```

#### endinterface

11/21/2024

```

`include "uvm_macros.svh"

`include "spi_pkg.sv"

`include "spi_interface.sv"

```

```

module tb_top;

import uvm_pkg::*;

import spi_pkg::*;

```

spi\_interface master (clock); // master int declaration

spi interface slave (clock); // slave int declaration

```

// SPI master core:

|spi spi master (

// UVM TB to DUT connection:

.wb clk i(clock),

.wb rst i(rstn),

.wb adr i(master.o wb addr[4:0]),

.wb dat i (master.o wb data),

.wb sel i (master.o wb sel),

.wb we i (master.o wb we),

.wb stb i (master.o wb stb),

.wb cyc i(master.o wb cyc),

.wb dat o(master.i wb data),

.wb ack o(master.i wb ack),

.wb err o(master.i wb err),

.wb int o(master.i wb int),

// master to slave connection:

.ss pad o(ss),

.sclk pad o(sclk),

.mosi pad o(mosi),

.miso pad i(miso),

.tip(master.tick)

);

```

```

initial begin

generate clock();

reset dut(); May not needed 'cause we can use test with reset phase

reg 2ints to config db();

run test();

end

itask generate clock();  always #25 clock = ~clock;

fork

forever begin

clock = 0;

#(25);

clock = 1;

#(25);

end

join none

endtask

```

```

itask reset_dut();

rstn <= 0;

repeat (25) @ (posedge clock);

rstn <= 1;

repeat (25) @ (posedge clock);

rstn = 0;

endtask

function void reg_2ints_to_config_db();

// Registers two interfaces in the configuration data base so that

// other blocks can use it retrived using get method

uvm_config_db #( virtual spi_interface)::set(null, "*", "m_if", master);

uvm_config_db #( virtual spi_interface)::set(null, "*", "s_if", slave);

endfunction</pre>

```

endmodule

```

Iclass wb bfm extends uvm object;

`uvm object utils (wb bfm)

[function new (string name = "wb bfm");

super.new(name);

-endfunction

static task wb reset;

input spi vif vif;

vif.o wb addr <= {5{1'bx}};</pre>

vif.o wb data <= {32{1'bx}};</pre>

vif.o wb cyc \leq 1'b0;

vif.o wb stb <= 1'bx;

vif.o wb we \leq 1'hx;

vif.o wb sel <= {4{1'bx}};</pre>

-endtask

```

```

static task wb_read;

input spi_vif vif;

input integer delay;

input logic [4:0] a;

output logic [31:0] d;

```

begin

```

// wait initial delay

repeat (delay) @(vif.monitor cb);

// assert wishbone signals

repeat (1) @(vif.monitor cb);

vif.monitor cb.o wb addr <= a;

vif.monitor cb.o wb data <= {32{1'bx}};

vif.monitor cb.o wb cyc <= 1'b1;

vif.monitor cb.o wb stb <= 1'b1;

vif.monitor cb.o wb we <= 1'b0;

vif.monitor cb.o wb sel <= {4{1'b1}};

@(vif.monitor cb);

// wait for acknowledge from slave

wait (vif.monitor cb.i wb ack == 1'b1)

// negate wishbone signals

repeat (1) @(vif.monitor cb);

vif.monitor cb.o wb cyc <= 1'b0;

vif.monitor cb.o wb stb <= 1'bx;

vif.monitor cb.o wb addr <= {5{1'bx}};

vif.monitor cb.o wb data <= {32{1'bx}};

vif.monitor cb.o wb we <= 1'hx;

vif.monitor cb.o wb sel <= {4{1'bx}};

d = vif.monitor cb.i wb data;

end

```

11/21/2024

endtask

```

static task wb_write;

input spi_vif vif;

input integer delay;

input logic [4:0] a;

input logic [31:0] d;

```

begin

endclass

```

// wait initial delay

repeat (delay) @(vif.drive cb);

// assert wishbone signal

vif.drive cb.o wb addr <= a;

vif.drive cb.o wb data <= d;

vif.drive cb.o wb cyc <= 1'b1;

vif.drive cb.o wb stb <= 1'b1;

vif.drive cb.o wb we <= 1'b1;

vif.drive cb.o wb sel \leq \{4\{1'b1\}\};

@(vif.drive cb);

// wait for acknowledge from slave

//@(vif.drive cb);

wait (vif.drive cb.i wb ack == 1'b1)

// negate wishbone signals

repeat (2) @(vif.drive cb);

vif.drive cb.o wb cyc <= 1'b0;

vif.drive cb.o wb stb <= 1'bx;

vif.drive cb.o wb addr <= {5{1'bx}};</pre>

vif.drive cb.o wb data <= {32{1'bx}};</pre>

vif.drive cb.o wb we <= 1'hx;

vif.drive cb.o wb sel <= {4{1'bx}};</pre>

end

endtask

```

11/21/2024

51

### **External Note**

- TASK:

- Write a BFM class used for transactions at SoC AMBA bus.

- Typical:

- AXI Bus

- ab\_bfm.svh

- or axi\_bfm.svh

- Specifications:

- <u>https://kolegite.com/EE\_library/datasheets\_and\_manuals/FPGA/A\_MBA/IHI0022H\_c\_amba\_axi\_protocol\_spec.pdf</u> (2021)

- Overview:

- <u>https://www.cis.upenn.edu/~cis5710/current/slides/13\_axi.pdf</u>

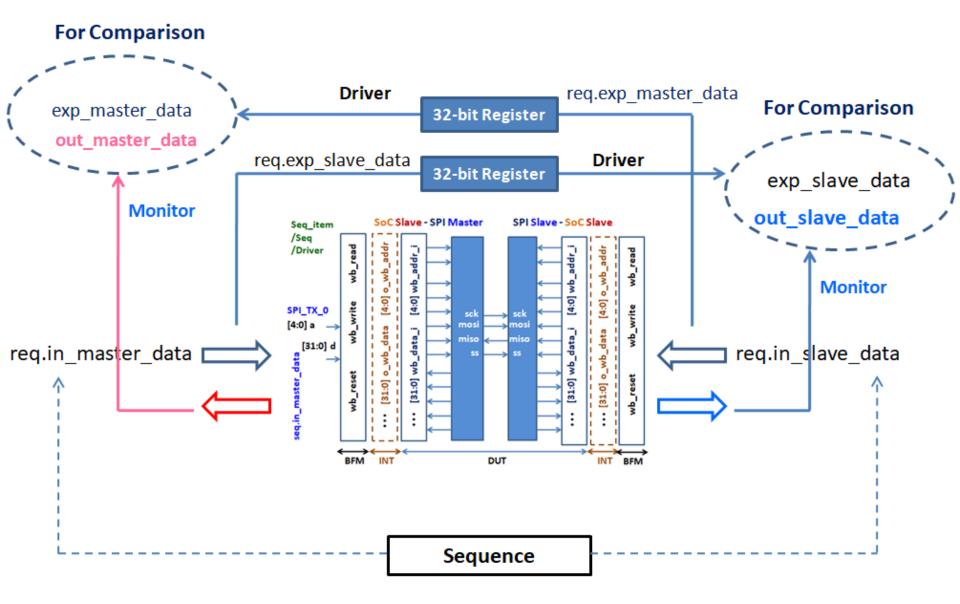

### class spi\_seq\_item extends uvm\_sequence\_item;

```

// Registers configuration:

rand logic [31:0] master ctrl reg;

rand logic [31:0] slave ctrl reg;

rand logic [31:0] divider reg;

rand logic [31:0] slave select reg;

rand logic [31:0] start dut reg;

// DUT output:

logic [31:0] out master data;

logic [31:0] out slave data;

// Expected data:

rand logic [31:0] exp master data;

rand logic [31:0] exp slave data;

// DUT input:

rand logic [31:0] in master data;

rand logic [31:0] in slave data;

```

```

`uvm object utils begin(spi seq item)

`uvm field int (master ctrl reg, UVM ALL ON)

`uvm field int(slave ctrl reg, UVM ALL ON)

`uvm field int (divider reg, UVM ALL ON)

`uvm field int(slave select reg, UVM ALL ON)

`uvm field int(start dut reg, UVM ALL ON)

`uvm field int (out master data, UVM ALL ON)

`uvm field int(out slave data, UVM ALL ON)

`uvm field int(exp master data, UVM ALL ON)

`uvm field int(exp slave data, UVM ALL ON)

`uvm field int (in master data, UVM ALL ON)

`uvm field int (in slave data, UVM ALL ON)

`uvm object utils end

function new (string name="spi seq item");

super.new (name);

endfunction

endclass

```

```

class spi seq extends uvm sequence#(spi seq item);

`uvm object utils(spi seq)

spi seq item req;

function new (string name="spi seq");

super.new(name);

endfunction

virtual task body();

req = spi seq item::type id::create("req");

start item(req);

//configure dut register();

set dut data();

finish item(req);

endtask

```

```

dvirtual function void configure_dut_register();

assert (req.randomize() with {req.master_ctrl_reg == 32'h00002208;

//32'b0010 0010 0000 1000

req.slave_ctrl_reg == 32'h00000200;//32'b0000000000000 (CTRL[9]=1'b1, Rx_NEG)

req.divider_reg == 32'h0000000; // DIVIDER = 0

req.slave_select_reg == 32'h0000001;//32'b000000000000001 (Slv needs the bit set)

req.start_dut_reg == 32'h00000320;});//32'b0000 0011 0010 0000

//0x20(char length)-32 bits; CTRL[9]=1,Rx_NEG; CTRL[8]=1,GO_BSY

endfunction

dvirtual function void set dut data();

```

```

assert (req.randomize() with {req.divider_reg == 32'h00000000;

req.master_ctrl_reg == 32'h00002208;

req.slave_ctrl_reg == 32'h00000200;

req.slave_select_reg == 32'h00000001;

req.start_dut_reg == 32'h00000320;

req.exp_master_data == req.in_slave_data; //

req.exp_slave_data == req.in_master_data;});//

endfunction

```

```

endclass

```

vvm\_analysis\_port #(seq\_item)

```

class spi driver extends uvm driver #(spi seq item);

`uvm component utils (spi driver)

spi vif m vif, s vif;

spi seq item packet;

uvm analysis port #(spi seq item) dut in pkt;

[function new (string name="spi driver", uvm component parent);

super.new(name, parent);

dut in pkt = new ("dut in pkt", this);

endfunction

function void build phase (uvm phase phase);

super.build phase(phase);

`uvm info (get full name(), "Build phase called in spi driver", UVM LOW)

if (!uvm config_db #(virtual spi_interface)::get(this, "", "m_if", m_vif))

`uvm_fatal("NO_VIF", {"virtual interface must be set for:", get_full_name(), ".m_vif"})

if (!uvm_config_db #(virtual spi_interface)::get(this, "", "s_if", s_vif))

`uvm fatal("NO VIF", {"virtual interface must be set for:", get full name(), ".s vif"})

endfunction

```

```

task run phase (uvm phase phase);

packet = spi seq item::type id::create("packet");

wb bfm::wb reset (m vif);

wb bfm::wb reset(s vif);

fork

forever begin

seq item port.get next item (req);

drive transfer(reg);

$cast(packet, req.clone());

packet = req;

dut in pkt.write(packet);

seq item port.item done();

wait(m vif.monitor cb.tick == 1'b0);

end

join none

endtask

task drive transfer (spi seq item seq);

wb bfm::wb write(m vif, 0, SPI DIVIDE, seq.divider reg); // set divider register

wb bfm::wb write(m vif, 0, SPI SS, seq.slave select reg); // set ss 0

wb bfm::wb write(m vif, 0, SPI TX 0, seq.in master data); // set master data register

wb bfm::wb write(m vif, 0, SPI CTRL, seq.master ctrl reg);// set master ctrl register

wb bfm::wb write(s vif, 0, SPI CTRL, seq.slave ctrl reg); // set slave ctrl register

wb bfm::wb write(s vif, 0, SPI TX 0, seq.in slave data); // set slave data register

wb bfm::wb write(m vif, 0, SPI CTRL, seq.start dut reg); // start data transfer

endtask

```

```

class spi monitor extends uvm monitor;

`uvm component utils(spi monitor)

spi vif m vif, s vif;

uvm_analysis_port #(seq_item)

spi seq item packet;

uvm analysis port#(spi seq item) dut out pkt;

function new (string name="spi monitor", uvm component parent);

super.new(name, parent);

dut out pkt = new("dut out pkt", this);

endfunction

function void build phase(uvm phase phase);

super.build phase(phase);

`uvm info(get full name(), "Build phase called in spi monitor", UVM LOW)

if (!uvm config db#(virtual spi interface)::get(this, "", "m if", m vif))

`uvm fatal("NO VIF", {"virtual interface must be set for:", get_full_name(), ".m_vif"})

if (!uvm config db#(virtual spi interface)::get(this, "", "s if", s vif))

`uvm fatal("NO VIF", {"virtual interface must be set for:", get full name(), ".s vif"})

endfunction

task run phase (uvm phase phase);

packet = spi seq item::type id::create("packet");

wait (m vif.monitor cb.tick ==1'b1) // wait to start

forever begin

wait (m vif.monitor cb.tick ==1'b0) // wait to complete

wb bfm::wb read(m vif, 1, SPI RX 0, packet.out master data);

wb bfm::wb read(s vif, 1, SPI RX 0, packet.out slave data);

dut out pkt.write(packet);

wait (m vif.monitor cb.tick ==1'b1); // wait to start

end

endtask

endclass

59

11/21/2024

```

```

class spi coverage extends uvm component;

`uvm component utils (spi coverage)

spi seq item c pkt;

extends uvm_subscriber #(spi_seq_item);

covergroup cov inst;

cp dut mosi: coverpoint c pkt.exp master data

bins byte0 7 = {[0:255]};

bins byte8 15 = { [256:65535] };

bins byte16 23 = {[65536:16777215]};

bins byte24 31 = {[16777216:$]};

endgroup

function new (string name="spi coverage", uvm component parent=null);

super.new(name, parent);

cov inst = new();

endfunction

function void perform coverage(spi seq item pkt);

this.c pkt = pkt;

cov inst.sample();

endfunction

```

```

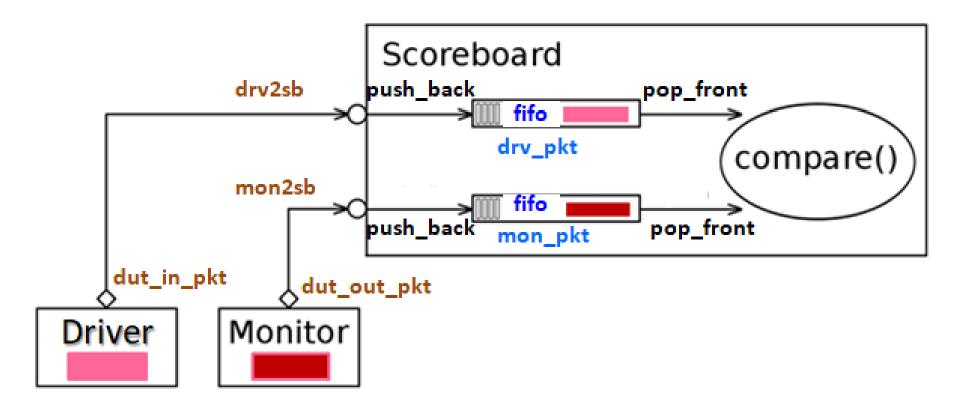

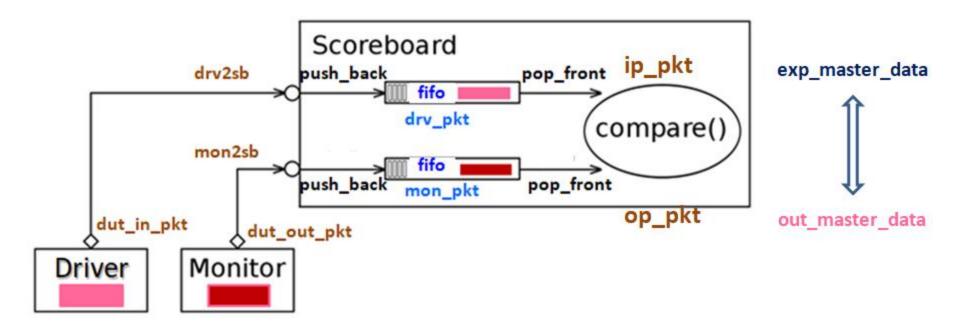

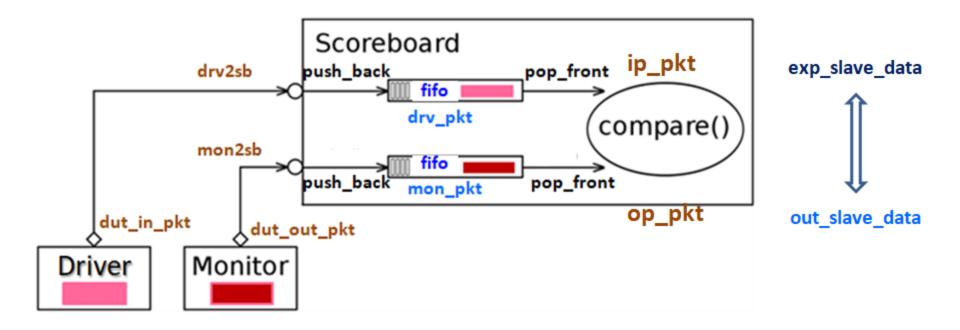

class spi scoreboard extends uvm scoreboard;

`uvm component utils (spi scoreboard)

uvm tlm analysis fifo #(spi seq item) drv2sb; //

uvm tlm analysis fifo #(spi seq item) mon2sb; //

spi seq item drv pkt[$]; // unbounded

spi seq item mon pkt[$]; // unbounded

spi seq item ip pkt;

spi seq item op pkt;

static string report tag;

spi coverage spi covg;

int pass = 0;

int fail = 0;

function new (string name="spi scoreboard", uvm component parent);

super.new(name, parent);

report tag = $sformatf("%0s", name);

drv2sb = new ("drv2sb", this);

mon2sb = new ("mon2sb", this);

endfunction

function void build phase (uvm phase phase);

super.build phase(phase);

`uvm info(get full name(), "Build phase called in spi scoreboard", UVM LOW)

spi covg = spi coverage::type id::create("spi covg", this);

endfunction

```

```

function void connect phase (uvm phase phase);

super.connect phase(phase);

'uvm info(get full name(), "Connect phase called in spi scoreboard", UVM LOW)

endfunction

task run phase (uvm phase phase);

forever begin

perform_check(ip_pkt, op_pkt);

perform coverage(ip pkt);

uvm test done.drop objection(this);

end

endtask

function void perform coverage (spi seq item pkt);

spi covg.perform coverage(pkt);

endfunction

function void perform check (spi seq item ip pkt, spi seq item op pkt);

forever begin

fork

drv2sb.get(ip pkt);

`uvm info("SB", "TRANSACTIONS FROM DRIVER", UVM NONE);

mon2sb.get(op pkt);

'uvm info("SB", "TRANSACTIONS FROM MONITOR", UVM NONE);

join

if (ip_pkt.exp_master_data == op_pkt.out_master_data && ip_pkt.exp_slave_data == op_pkt.out_slave_data)

begin

`uvm info(get full name(), "Master PASSED", UVM MEDIUM)

`uvm info(get full name(), "Slave PASSED", UVM MEDIUM)

pass++;

end

else

begin

`uvm info(get full name(), $sformatf("Slave FAILED: exp data=%0h and out data=%0h", ip pkt.exp slave data, op pkt.out slave data), UVM MEDIUM)

`uvm info(get full name(), $sformatf("Master FAILED: exp data=%0h and out master data=%0h", ip pkt.exp master data, op pkt.out master data), UVM MEDIUM)

fail++;

end

Note

end

endfunction

```

function void extract\_phase(uvm\_phase phase);

endfunction

function void report phase(uvm phase phase); if (fail==0) begin uvm report info("Scoreboard Report", \$sformatf("Transactions PASS = %0d FAIL = %0d", pass, fail), UVM MEDIUM); \$display("-----"); \$display("-----"); end else begin uvm report info("Scoreboard Report", \$sformatf("Trasactions PASS = %0d FAIL = %0d", pass, fail), UVM MEDIUM); \$display("-----"): Sdisplay("-----"): end

endfunction

```

class spi agent extends uvm agent;

`uvm component utils(spi agent)

spi sequencer sequencer;

spi monitor monitor;

spi driver driver;

spi vif m vif, s vif;

function new (string name="spi agent", uvm component parent);

super.new(name, parent);

endfunction

function void build phase (uvm phase phase);

super.build phase(phase);

`uvm info(get full name(), "Build phase called in spi agent", UVM LOW)

if (!uvm config db#(virtual spi interface)::get(this, "", "m if", m vif))

`uvm fatal("NO VIF", {"virtual interface must be set for:", get full name(), ".m vif"})

if (!uvm config db#(virtual spi interface)::get(this, "", "s if", s vif))

`uvm fatal("NO VIF", {"virtual interface must be set for:", get full name(), ".s vif"})

sequencer = spi sequencer::type id::create("sequencer", this);

driver = spi driver::type id::create("driver", this);

driver.m vif = m vif;

driver.s vif = s vif;

monitor = spi monitor::type id::create("monitor", this);

monitor.m vif = m vif;

monitor.s vif = s vif;

endfunction

function void connect phase (uvm phase phase);

super.connect phase(phase);

`uvm info(get full name(), "Connect phase called in spi agent", UVM LOW)

driver.seg item port.connect(sequencer.seg item export);

endfunction

```

```

endclass

```

```

class spi env extends uvm env;

`uvm component utils (spi env)

spi agent agent;

spi scoreboard scoreboard;

function new (string name="spi env", uvm component parent);

super.new(name, parent);

endfunction

function void build phase (uvm phase phase);

super.build phase(phase);

`uvm info(get full name(), "Build phase called in spi environment", UVM LOW)

// Build agent and scoreboard components:

agent = spi agent::type id::create("agent", this);

scoreboard = spi scoreboard::type id::create("scoreboard", this);

endfunction

function void connect phase (uvm phase phase);

super.connect phase(phase);

`uvm info(get full name(), "Connect phase called in spi environment", UVM LOW)

// Connect the analysis ports at driver and monitor with scoreboard:

agent.driver.dut in pkt.connect(scoreboard.drv2sb.analysis export);

agent.monitor.dut out pkt.connect(scoreboard.mon2sb.analysis export);

endfunction

```

```

class spi test extends uvm test;

`uvm component utils(spi test)

spi env env;

spi seq t seq;

function new (string name="spi test", uvm component parent);

super.new(name, parent);

endfunction

function void build phase(uvm phase phase);

super.build phase(phase);

`uvm info(get full name(), "Build phase called in spi test", UVM LOW)

// Build environment component:

env = spi env::type id::create("env", this);

endfunction

function void connect phase (uvm phase phase);

super.connect phase (phase);

`uvm info (get full name(), "Connect phase called in spi test", UVM LOW)

endfunction

```

```

task reset phase (uvm phase phase);

phase.raise objection(this);

rstn <= 0:

repeat (25) @ (posedge clock);

rstn <= 1;

repeat (25) @ (posedge clock);

rstn = 0:

phase.drop objection(this);

endtask

virtual task main phase (uvm phase phase);

`uvm info (get full name(), "in main phase", UVM LOW)

phase.raise objection(this);

t seq = spi seq::type id::create("t seq");

repeat(100)

t seq.start(env.agent.sequencer);

phase.drop objection(this);

```

```

endtask

```

```

package spi_pkg;

```

import uvm\_pkg::\*;

`include "uvm\_macros.svh"

`include "tb defines.svh" `include "spi seq item.svh" `include "wb bfm.svh" `include "spi driver.svh" `include "spi monitor.svh" `include "spi sequencer.svh" `include "spi agent.svh" `include "spi coverage.svh" `include "spi scoreboard.svh" `include "spi seq.svh" `include "spi env.svh" `include "spi test.svh"

### endpackage

```

// Register address values:

2

3

parameter SPI RX 0 = 5'h0;

4

parameter SPI RX 1 = 5'h4;

5

parameter SPI RX 2 = 5'h8;

6

parameter SPI RX 3 = 5'hc;

7

8

parameter SPI TX 0 = 5'h0; // 0000 0000

9

parameter SPI TX 1 = 5'h4; // 0000 0100

parameter SPI TX 2 = 5'h8; // 0000 1000

10

11

parameter SPI TX 3 = 5'hc; // 0000 1100

12

parameter SPI CTRL = 5'h10; // 0001 0000

parameter SPI DIVIDE = 5'h14; // 0001 0100

13

parameter SPI SS = 5'h18; // 0001 1000

14

15

16

logic clock, rstn;

17

wire logic sclk, mosi, miso;

wire logic [31:0]ss;

18

19

logic tip;

20

21

// Virtual interface:

22

typedef virtual spi interface spi vif;

```

### **Backup Slide**

class spi\_sequencer extends uvm\_sequencer #(spi\_seq\_item); `uvm\_component\_utils(spi\_sequencer)

function new (string name="spi\_sequencer", uvm\_component parent);

super.new(name, parent);

endfunction

```

2

set RTL ./dut

3

# Library and mapping: ------

4

vlib work

5

6

vmap work work

7

8

# Compilation: -----

vlog $RTL/*.v +acc +cover=bcefst

9

vlog spi interface.sv -timescale 1ns/10ps

10

11

vlog spi pkg.sv

12

vlog tb top.sv +acc +cover=bcefst

13

14

# Simulation: ------

vsim -coverage -novopt tb_top +UVM_TESTNAME=spi_test

15

16

# Coverage report: ------

17

18

# Coverage save ucdb file:

19

coverage save -onexit -assert -directive -cvg -codeAll spi test.ucdb

20

21

# Coverage reports with html and text files:

22

vcover report -html spi test.ucdb -htmldir covhtmlreport

vcover report -file cov report.txt spi test.ucdb

23

24

25

add wave -r sim:/tb top/*

26 run -all

```

#### 11/21/2024

## **Thank You**