# **True DPRAM – UVM Testbench** For whom can know how to program

Tuan Nguyen-viet

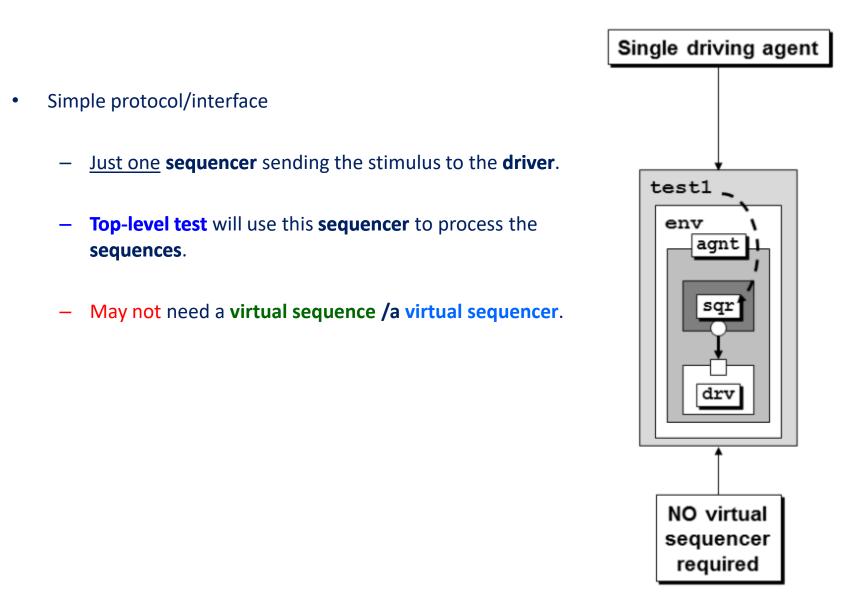

# **Simple Protocol/Interface**

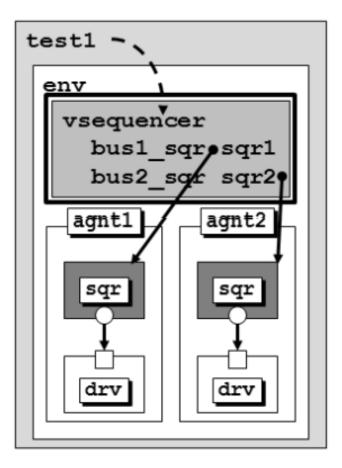

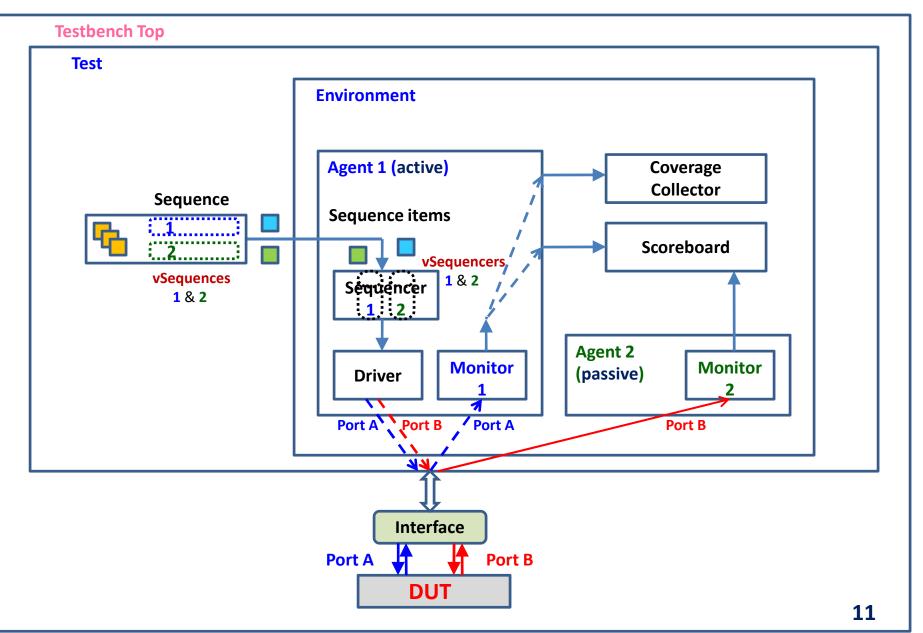

# **Two or More Interfaces/Protocols**

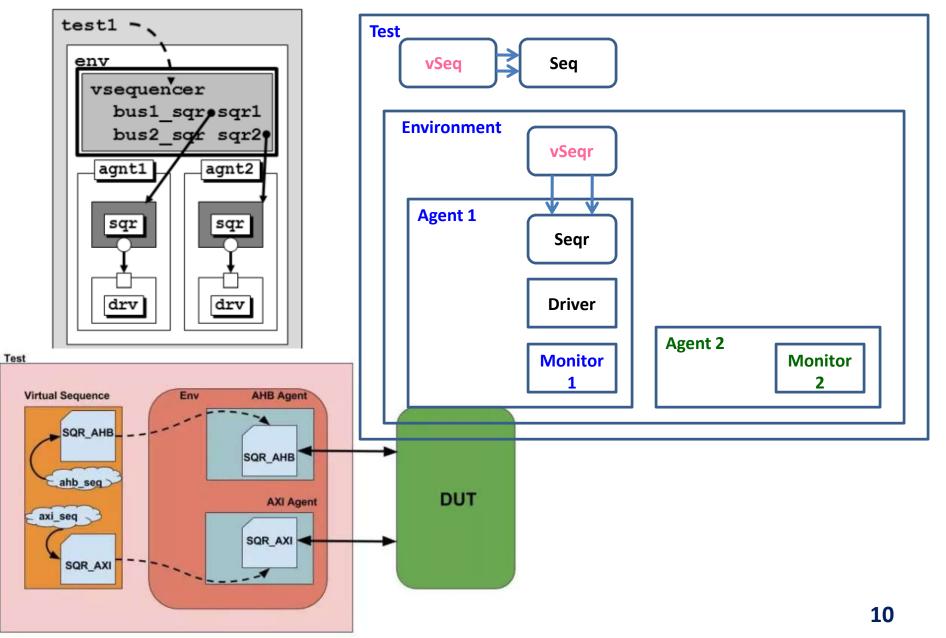

- DUT is having 2 different interface ports,

- There would be 2 Agents serving each interface port inside the UVM Testbench.

- Virtual Sequence will co-ordinate and synchronize the Transactions (sequence items)

- for the 2 **Agents** to generate the simulation.

- Virtual Sequence acts like a <u>Controller</u> of the simulation data being generated for the **DUT**.

- From top-level test,

- need a way to control two sequencers.

- Jusing a virtual sequencer and virtual sequences.

# **Two or More Interfaces/Protocols (2)**

- In **SoC**: <u>different modules</u> that interact with <u>different protocols</u>.

- need different drivers to drive corresponding interfaces.

- keep separate **agents** to handle the different protocols.

- execute sequences on corresponding sequencers.

- <u>multiple cores</u> in **SoC**.

- multiple cores present in SoC that can

- *handle* different operations *on input* provided

- and *respond to* the device/chip differently.

- − → different sequence execution becomes important on different sequencers.

- It is recommended to use a virtual sequencer/sequence

- 1. if we have multiple **agents**

- 2. and stimulus coordination is required.

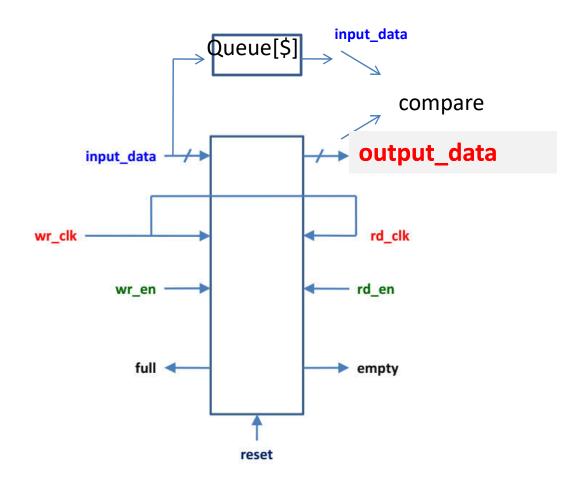

#### **SFIFO**

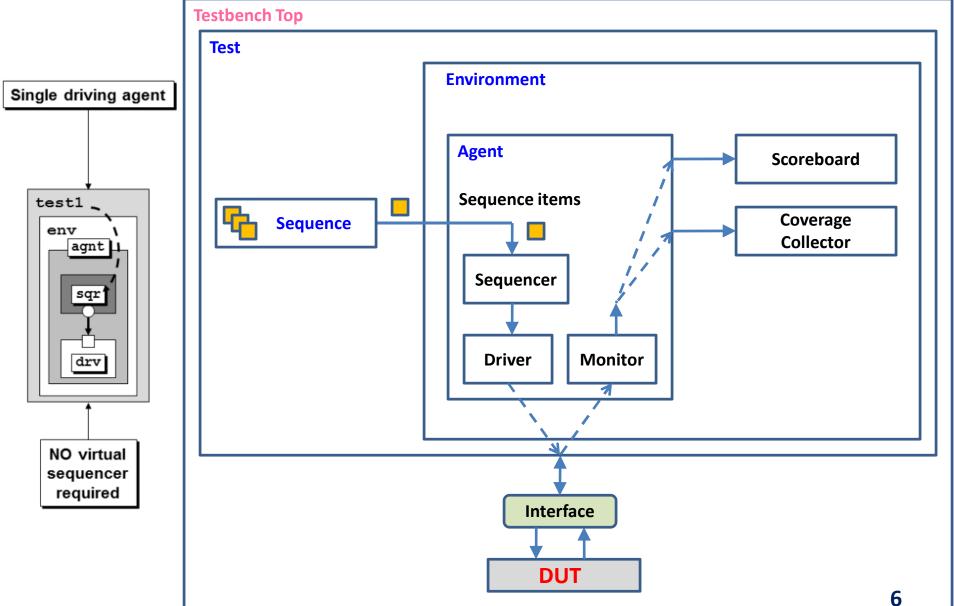

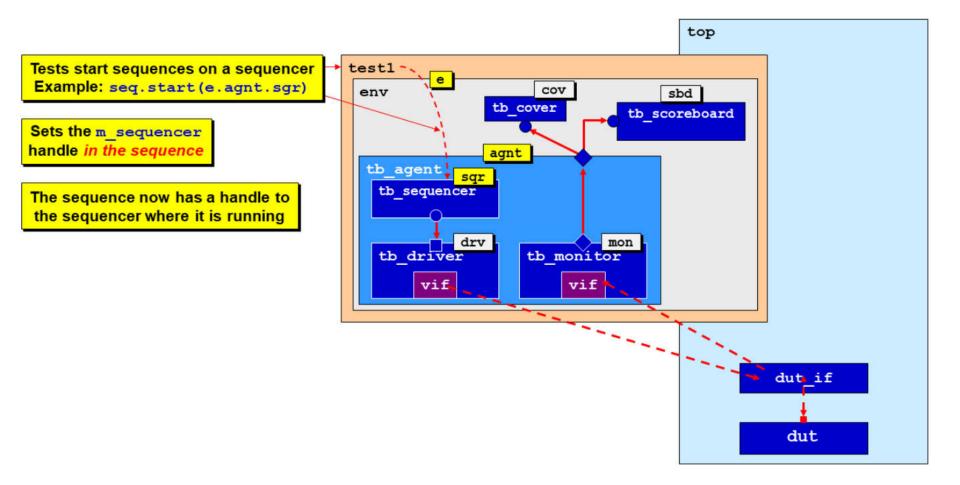

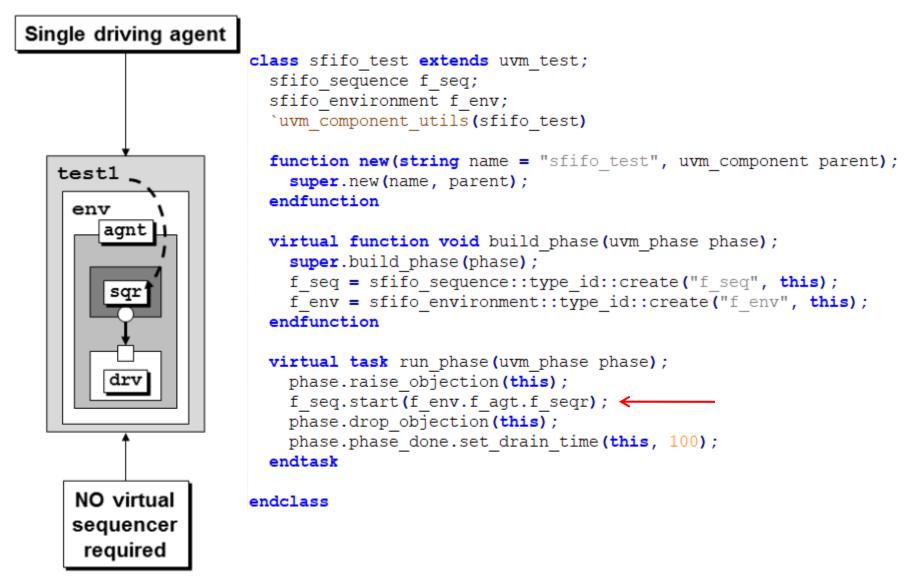

# **UVM - Simple Architecture w/ Single Agent**

# UVM - Simple Architecture w/ Single Agent (2)

REF: Understanding the UVM m\_sequencer, p\_sequencer, handles, and the `uvm\_declare\_p\_sequencer Macro, by Clifford E. Cummings

# **SFIFO UVM Testbench**

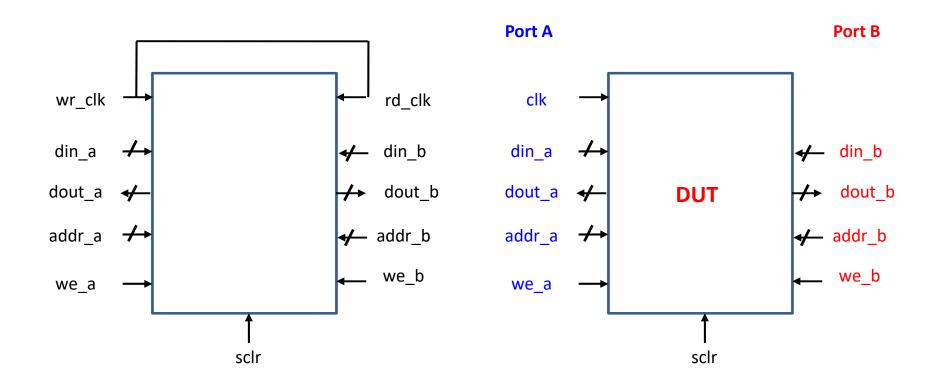

## **DUT – True DPRAM**

Sample: We will do a UVM Testbench for TDPRAM shown above.

## **UVM - Simple Architecture w/ Two Agents**

# UVM - Simple Architecture w/ Two Agents (A1 and B2)

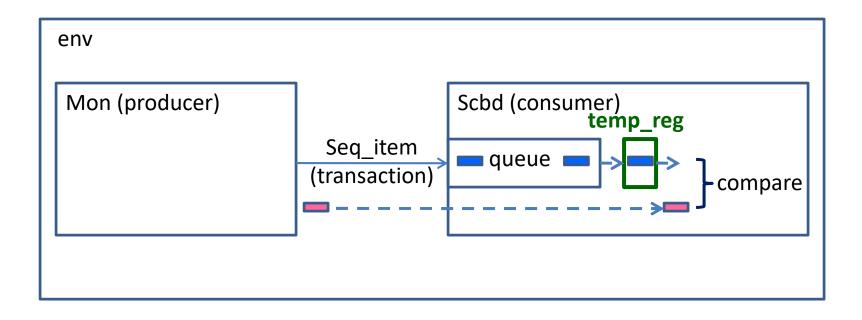

#### **FIFO at Scoreboard**

#### **SV-Queue FIFO**

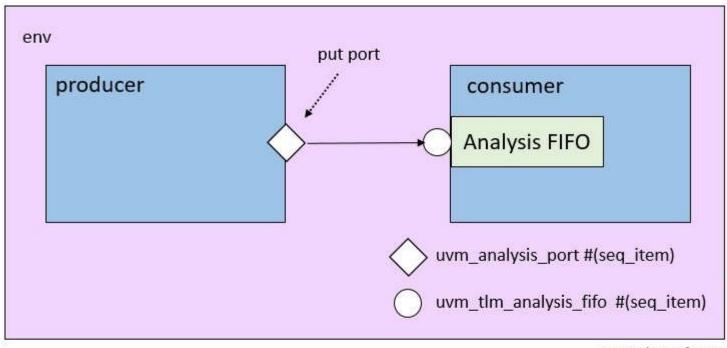

# **TLM Analysis FIFO**

www.vlsiverify.com

uvm\_tlm\_analysis\_fifo

# **Producer (e.g. Monitor)**

```

class producer extends uvm component;

seq item req;

uvm analysis port #(seq item) a port;

`uvm component utils(producer)

function new(string name = "producer", uvm component parent = null);

super.new(name, parent);

a port = new("a port", this);

endfunction

task run phase(uvm phase phase);

super.run phase(phase);

repeat(10) begin

req = seq_item::type_id::create("req");

assert(req.randomize());

a port.write(reg);

`uvm info(get name(), $sformatf("Send value = %0h", req.value), UVM_NONE);

#5;

end

endtask

endclass

```

# **Consumer (e.g. Scoreboard)**

```

class consumer extends uvm component;

seq item req;

uvm_tlm_analysis_fifo #(seq_item) tlm_a_fifo;

`uvm component utils(consumer)

function new(string name = "consumer", uvm_component parent = null);

super.new(name, parent);

tlm_a_fifo = new("tlm_a_fifo", this);

endfunction

task run phase(uvm phase phase);

super.run phase(phase);

repeat(10) begin

#10;

tlm_a_fifo.get(req);

`uvm info(get type name(), $sformatf("Received value = %0h", req.value), UVM NONE);

end

endtask

endclass

```

#### **Virtual Sequence and Virtual Sequencer**

## **Virtual Sequence and Virtual Sequencer**

- A virtual sequence starts multiple sequences on different sequencers.

- Virtual sequencer controls other sequencers

- and it is not attached to any **driver**.

- A virtual sequence is usually executed on the virtual sequencer.

# Why are the virtual\_sequence and virtual\_sequencer named virtual?

- System Verilog has virtual methods, virtual interfaces, and virtual classes.

- "virtual" keyword is common in all of them.

- But, virtual\_sequence and virtual\_sequencer do not require any virtual keyword.

- UVM does not have uvm\_virtual\_sequence and uvm\_virtual\_sequencer as base classes.

- A virtual sequence is derived from uvm\_sequence.

- A virtual\_sequencer is derived from uvm\_sequencer as a base class.

- Virtual sequencer controls other sequencers.

- It is not attached to any **driver** and can not process any **sequence\_items** too.

- Hence, it is named virtual.

Backup Slide 1

#### DIFFERENCE BETWEEN LOGIC AND BIT IN SYSTEMVERILOG

# Difference b/w logic and bit in SystemVerilog

In SystemVerilog, "logic" and "bit" are two different data types with distinct characteristics:

- 1. logic: The logic data type is a multi-valued logic type that can represent values beyond the traditional binary 0 and 1.

- It can represent the following values: 0, 1, X (unknown), and Z (high-impedance).

- The logic data type is the most commonly used data type in SystemVerilog

- and is the *recommended data type* for general use.

- 2. bit: The bit data type is a binary data type that can only represent the values 0 and 1.

- It is a more compact representation compared to logic,

- as it does not have the additional values of X and Z.

- The bit data type is typically used for Boolean or single-bit operations

- where the additional values provided by logic are not required.

# Difference b/w logic and bit in SystemVerilog (2)

The main differences between logic and bit are:

- **1. Supported Values**: logic can represent 0, 1, X, and Z, while bit can only represent 0 and 1.

- 2. Memory Usage: bit is more *memory-efficient* than logic

- because bit only requires a single bit of storage,

- whereas logic requires more memory to represent the additional values.

- **3.** Functionality: logic is more versatile

- and can be used in a wider range of applications,

- while bit is better suited for simple Boolean operations.

- In general, you should use logic as the default data type in SystemVerilog

- unless you have a specific reason to use bit,

- such as when you *need to optimize memory usage* or perform simple Boolean operations.

Backup Slide 2

**MODPORTS IN SV**

# **Modports in SV**

- **Modports** are a part of an **interface** that helps define the direction of signals.

- But we can also define the direction of signals within the **interface**,

- so what is the need for **modports**?

- We can see how **modports** help us organize signals in *complex designs* as well as *testbenches*.

# What are modports?

- **Modports** can be considered as a sub-entity of **interface** which defines a particular direction to the signals.

- In an interface, there can be many modports

- and all **modports** can define different directions to the signal.

#### Syntax:

modport <modport\_name> (<direction> <signal\_name [range]>, <direction> <signal\_name [range]>, ...);

modport <name> ( input <port\_list>, output <port\_list>);

modport TB (output a,b, en, input out, ack);

modport RTL (input clk, reset, a,b, en, output out, ack);

#### Interface

```

interface mult_if (input logic clk, reset);

logic [7:0] a, b;

logic [15:0] out;

logic en;

logic ack;

```

module multiplier(mult if inf);

```

modport TB (output a,b, en, input out, ack);

modport RTL (input clk, reset, a,b, en, output out, ack);

```

#### DUT (.sv)

```

always@(posedge inf.clk or posedge inf.reset) begin

if(inf.reset) begin

inf.out <= 0;

inf.ack <= 0;

end

else if(inf.en) begin

inf.out <= inf.a * inf.b;

inf.ack <= 1;

end

else inf.ack <= 0;

end

else inf.ack <= 0;

end

```

# **Need for modports**

An interface is an entity that helps connect testbenches to

- designs

- or different modules of a design.

For example, let's consider the simple scenario of connecting a testbench to a design.

- Any inputs in the design need to be driven by the testbench.

- So, the signals that are *inputs for the design* are *outputs for the testbench*.

- However, inside an **interface**,

- the same signal cannot take on two different directions.

- This is where **modports** become **helpful**.

- We can define <u>two</u> **modports** inside the **interface**.

- One will define the *directions* with respect to *the design*,

- and the other will define the *directions* with respect to *the testbench*.

# Need for modports (2)

- We can see that complex testbenches often have *drivers* and *monitors*.

- For a driver to drive signals, the direction would be *output*,

- but a monitor, as its name suggests, needs to monitor the signals and thus all the signals will be *inputs* in this case.

- This is another scenario where **modports** are helpful.

- This is the main reason why we use **logic** as a data type for signals inside.

- If we used **reg** or **wire**,

- then it would be difficult to make it behave as both input and output

- without worrying about the *driver* load issue.

# How to define port directions ?

```

interface myBus (input clk);

1

logic [7:0] data;

2

logic enable;

3

4

// From TestBench perspective, 'data' is input and 'write' is output

5

modport TB (input data, clk, output enable);

6

7

// From DUT perspective, 'data' is output and 'enable' is input

8

modport DUT (output data, input enable, clk);

9

endinterface

10

```

## m\_sequencer and p\_sequencer – Difference

- One of *the most confusing UVM stuff* is about m\_sequencer and p\_sequencer and the difference between the two.

- In reality, its just a game of **polymorphism**.

- Referring to some forum answer, m\_sequencer is a *generic sequencer pointer* of type uvm\_sequencer\_base.

- It will always exist for a **uvm\_sequence**

- and is initialized when the **sequence** is started.

- The p\_sequencer is a type specific sequencer pointer, created by registering the sequence to a sequencer using the `uvm\_declare\_p\_sequencer macros.

- Being type specific,

- you will be able to access anything added to the sequencer (i.e. pointers to other sequencers, etc.).

- p\_sequencer will not exist if the `uvm\_declare\_p\_sequencer macros isn't used.

## **Thank You**