# UVM (Universal Verification Methodology) For SW Engineers

Tuan Nguyen-viet

## Challenges of verifying complex systems – An Example

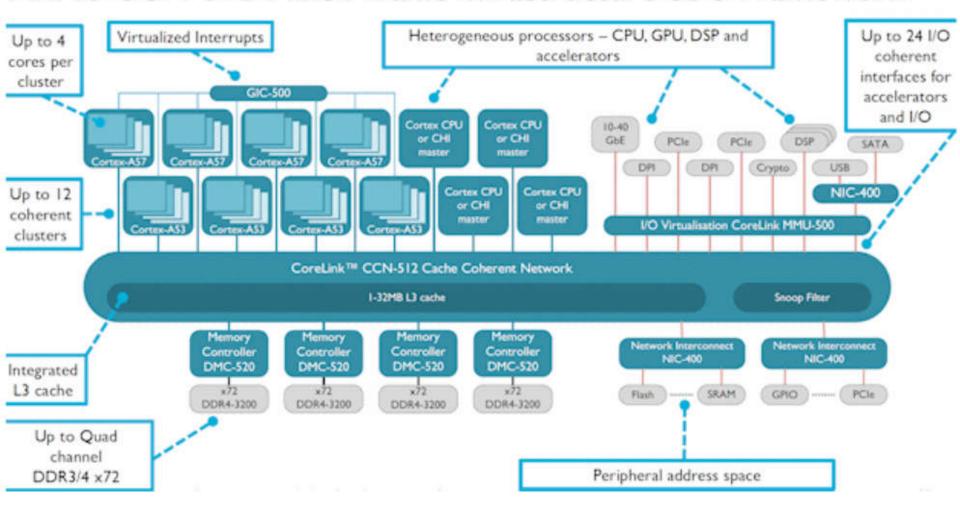

### ARM's CCN-512 Mixed Traffic Infrastructure SoC Framework

## Challenges of verifying complex systems (2)

- Typical processor development from scratch could be 100s of engineering years

- Requires parallel developments across multiple sites,

- and it takes a large team to verify a processor

- The typical method is to divide and conquer,

- partitioning the whole CPU into smaller units

- and verify those units,

- then reuse the checkers and stimulus at a higher level

- The challenges are numerous

- Reuse of code becomes an absolute key to avoid duplication of work

- It is essential to have the ability to integrate an external IP

- This requires rigorous planning, code structure, & lockstep development

- Standardization becomes a key consideration

- UVM can help solve this

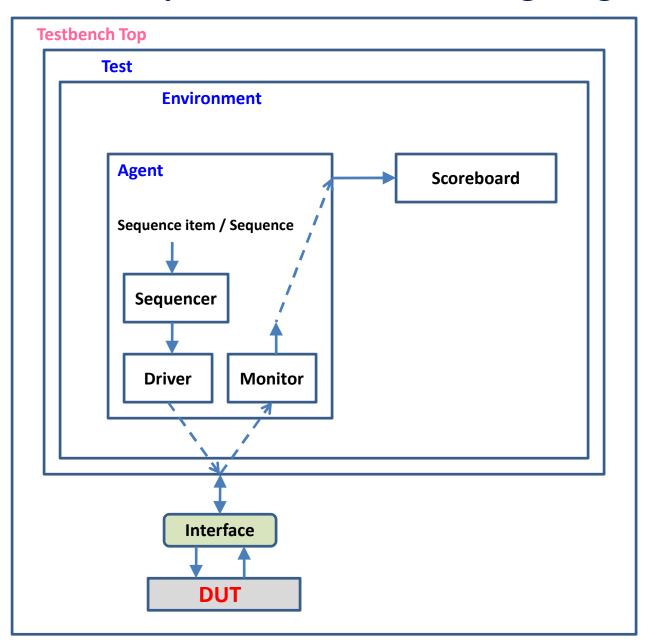

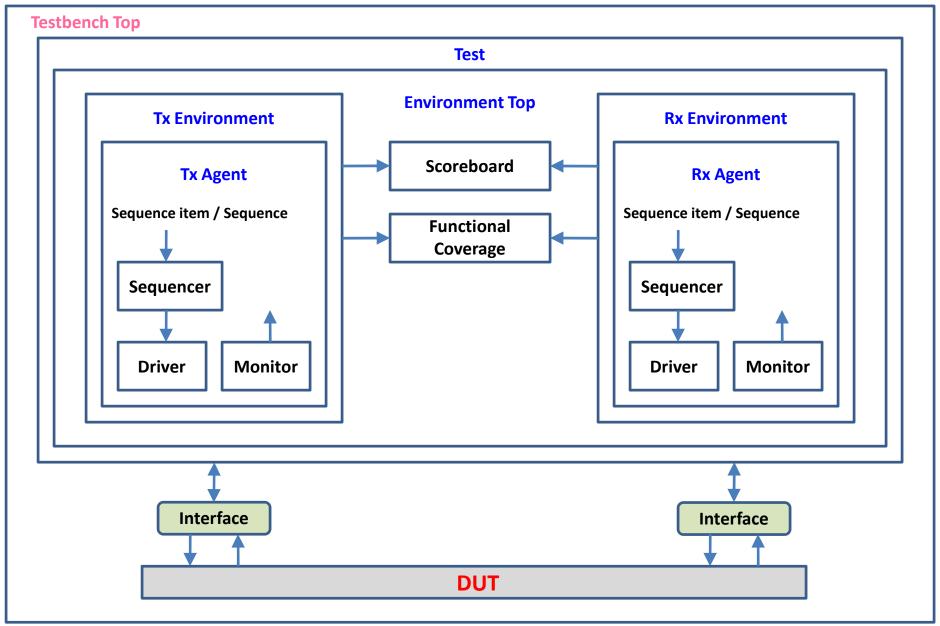

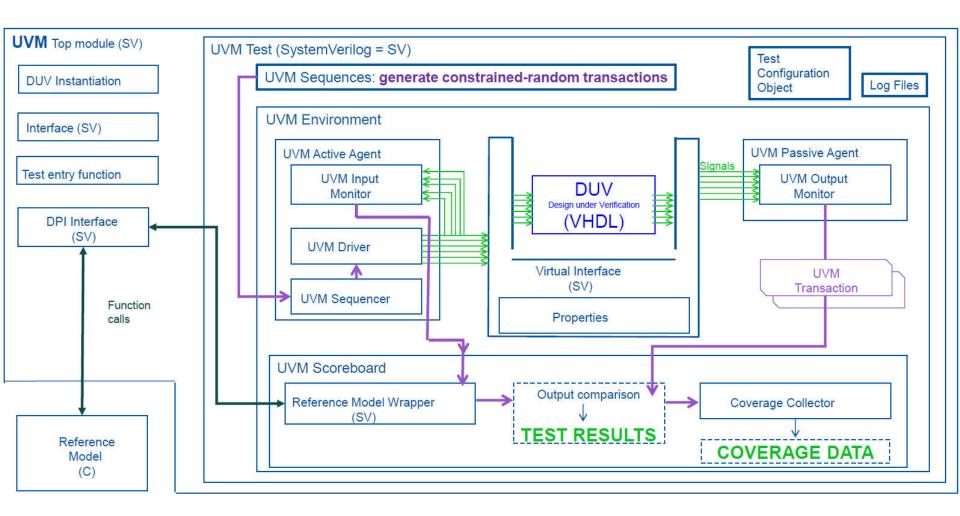

# **Key Components of a UVM Testbench**

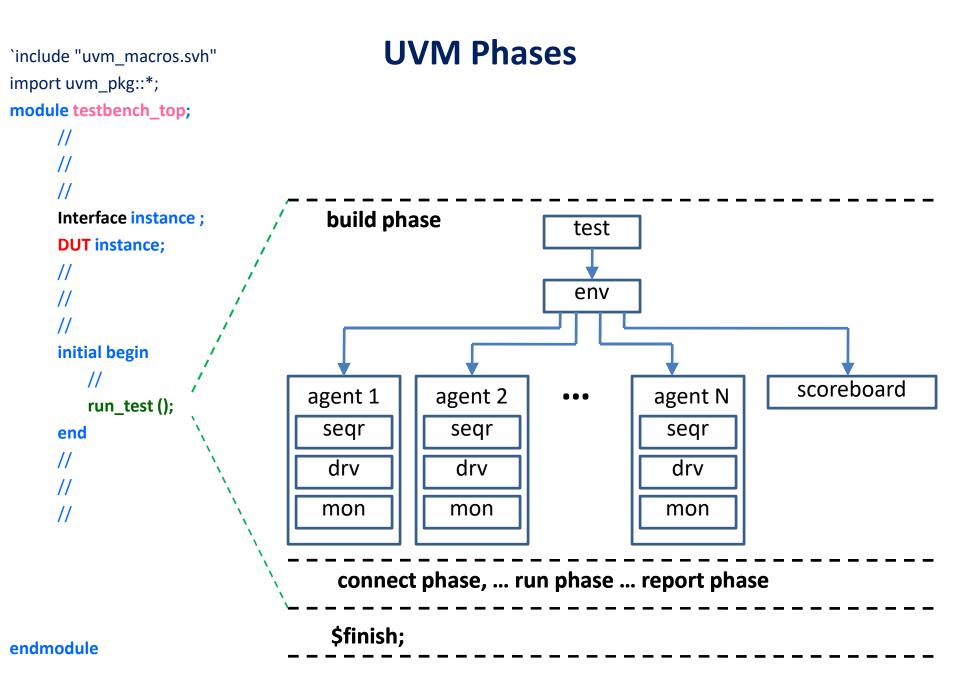

## **UVM Testbench Top**

- All verification components, interfaces and DUT

- are instantiated in a top level module called testbench.

- It is a <u>static container</u> to hold everything required to be simulated

- and becomes the <u>root node</u> in the hierarchy.

- This is usually named tb or tb\_top

- although it can assume any other name.

- **Simulators** (e.g. NCSIM, Questasim, etc.) typically need to know the **top** level module

- so that each can

- analyze components within the top module

- and elaborate the design hierarchy.

## **UVM Testbench Top**

- The testbench top is a <u>static container</u>

- that has an instantiation of DUT and interfaces.

- The interface instance connects with DUT signals in the testbench top.

- The clock is generated and initially reset is applied to the DUT.

- It is also passed to the interface handle.

- An interface is stored in the uvm\_config\_db

- using the set method

- and it can be retrieved down the hierarchy

- using the get method.

- UVM testbench top is also used to trigger a test

- using run\_test() call.

- REF: <a href="https://vlsiverify.com/uvm/uvm-testbench-top/">https://vlsiverify.com/uvm/uvm-testbench-top/</a>

# **UVM - Simple Architecture w/ Single Agent**

## **Key Components of a UVM Testbench**

## **UVM** tb top

- Typical Testbench\_top contains,

- DUT instance

- interface instance

- run\_test() method

- virtual interface set config\_db

- clock and reset generation logic

- wave dump logic

```

module testbench_top;

//clock and reset signal declaration

bit clk;

bit reset;

//clock generation

always #5 clk = ~clk;

//reset Generation

initial begin

reset = 1;

#5 reset =0;

input_data

output_data

end

//creating instance of interface, in order to connect DUT and testcase

sync_fifo_if intf(clk,reset);

//DUT instance, interface signals are connected to the DUT ports

rd_clk

wr_clk

sync_fifo DUT (

.clk(intf.clk),

.reset(intf.reset),

rd en

wr_en

.full(intf.full),

.empty(intf.empty),

.wr_en(intf.wr_en),

full <

empty

.rd_en(intf.rd_en),

.input_data(intf.wdata),

.output_data(intf.rdata)

reset

//enabling the wave dump

initial begin

uvm_config_db#(virtual sync_fifo_if)::set(uvm_root::get(),"*","sync_fifo_intf",intf);

$dumpfile("dump.vcd"); $dumpvars;

end

initial begin

run_test();

end

```

endmodule

**12**

### **UVM TestBench Architecture**

- To maintain **uniformity** in naming the components/objects,

- all the component/object name's are starts with sync\_fifo\_\*.

**Sequence Item/Transaction**

## **UVM TB Architecture: Sequence Item/Transaction**

- Sequence Item is the same as a Transaction

- Examples: packet, AXI transaction, pixel

- Fields required to generate the stimulus are declared in the sequence item.

- 1. sequence item is written by extending <a href="https://www.sequence\_item">www\_sequence\_item</a>,

```

class sync_fifo_seq_item extends uvm_sequence_item;

//Utility macro

`uvm_object_utils(sync_fifo_seq_item)

//Constructor

function new(string name = "sync_fifo_seq_item");

super.new(name);

endfunction

endclass

```

## **UVM TB Architecture: Sequence Item/Transaction (2)**

2. Declaring the fields in sync\_fifo\_seq\_item,

```

class sync fifo seq item extends uvm sequence item;

//data and control fields

bit

full;

bit empty;

bit wr_en;

bit rd en;

bit [15:0] wdata;

bit [15:0] rdata;

//Utility macro

`uvm_object_utils(sync_fifo_seq_item)

//Constructor

function new(string name = " sync_fifo_seq_item ");

super.new(name);

endfunction

endclass

```

## **UVM TB Architecture: Sequence Item/Transaction (3)**

3. To generate the random stimulus, declare the fields as rand.

```

class sync fifo seq item extends uvm sequence item;

//data and control fields

input data

output data

bit

full;

bit

empty

rand bit

wr_en;

rd_clk

rand bit rd en;

rd en

rand bit [15:0] wdata;

bit [15:0] rdata;

full

empty

//Utility macro

`uvm_object_utils(sync_fifo_seq_item)

reset

//Constructor

function new(string name = " sync_fifo_seq_item ");

super.new(name);

endfunction

endclass

```

## **UVM TB Architecture: Sequence Item/Transaction (4)**

4. In order to use the uvm\_object methods (copy, compare, pack, unpack, record, print, and etc ),

all the fields are registered to uvm\_field\_\* macros.,

```

class sync fifo seq item extends uvm sequence item;

//data and control fields

bit full, empty;

rand bit wr en;

rand bit rd en;

rand bit [7:0] wdata;

bit [7:0] rdata;

//Utility and Field macros,

'uvm object utils begin(sync fifo seg item)

'uvm field int(wr en, UVM ALL ON)

'uvm field int(rd en, UVM ALL ON)

'uvm field int(wdata, UVM ALL ON)

'uvm object utils end

//Constructor

function new(string name = "sync_fifo_seq_item");

super.new(name);

endfunction

endclass

```

## **UVM TB Architecture: Sequence Item/Transaction (5)**

5. Either write or read operation will be performed at once,

so the **constraint** is added to generate wr\_en and rd\_en.

```

class sync_fifo_seq_item extends uvm_sequence_item;

//data and control fields

bit full, empty;

rand bit wr_en;

rand bit rd en;

rand bit [7:0] wdata;

bit [7:0] rdata;

//Utility and Field macros,

`uvm object utils begin(sync_fifo_seq_item)

'uvm field int(wr en, UVM ALL ON)

'uvm field int(rd en, UVM ALL ON)

'uvm field int(wdata, UVM ALL ON)

'uvm object utils end

//Constructor

function new(string name = "sync fifo seq item");

super.new(name);

endfunction

//constaint, to generate any one among write and read

constraint wr rd c { wr en != rd en; };

endclass

```

## **UVM TB Architecture: Sequence Item/Transaction (6)**

#### Complete sync\_fifo\_seq\_item code.

```

class sync_fifo_seq_item extends uvm_sequence_item;

//data and control fields

bit

full;

bit

empty;

rand bit

wr en;

rand bit

rd en;

rand bit [7:0] wdata;

bit [7:0] rdata;

//Utility and Field macros,

`uvm_object_utils_begin(sync_fifo_seq_item)

'uvm field int(wr en,UVM ALL ON)

`uvm_field_int(rd_en,UVM_ALL_ON)

'uvm field int(wdata,UVM ALL ON)

'uvm object utils end

//Constructor

function new(string name = "sync fifo seg item");

super.new(name);

endfunction

//constaint, to generate any one among write and read

constraint wr rd c { wr en != rd en; };

endclass

```

# **Sequence**

## **UVM TB Architecture: Sequence**

- UVM Sequence is a collection/list of UVM Sequence Items.

- UVM Sequence generates the <u>stimulus</u>

- and sends to UVM Driver via UVM Sequencer.

- A UVM Agent can have any number of UVM Sequences.

## **UVM TB Architecture: Sequence (2)**

1. A sequence is written by extending the <a href="https://www.sequence">uvm\_sequence</a>,

```

class sync_fifo_sequence extends uvm_sequence # (sync_fifo_seq_item);

`uvm_sequence_utils(sync_fifo_sequence, sync_fifo_sequencer)

//Constructor

function new(string name = "sync_fifo_sequence");

super.new(name);

endfunction

endclass

```

## **UVM TB Architecture: Sequence (3)**

Logic to generate and send the sequence\_item is added inside the body() method,

```

class sync_fifo_sequence extends uvm_sequence # (sync_fifo_seq_item);

'uvm sequence utils(sync fifo sequence, sync fifo sequencer)

//Constructor

function new(string name = "sync fifo sequence");

super.new(name);

endfunction

virtual task body();

req = sync_fifo_seq_item ::type_id::create("req");

wait for grant();

req.randomize();

send_request(req);

wait for item done();

endtask

endclass

```

# **Sequencer**

## **UVM TB Architecture: Sequencer**

- Sequencer is written by extending uvm\_sequencer,

- there is no extra logic required to be added in the sequencer.

- 1. sequence item is written by extending <a href="https://www.sequence\_item">uvm\_sequence\_item</a>,

```

class sync_fifo_sequencer extends uvm_sequencer #(sync_fifo_seq_item);

//Utility macro

`uvm_object_utils(sync_fifo_sequencer)

//Constructor

function new(string name, uvm_component parent);

super.new(name);

endfunction

endclass

```

## **UVM TB Architecture: Sequencer (2)**

- A UVM sequencer connects a UVM Sequence to the UVM Driver

- It sends a transaction from the Sequence to the Driver

- It sends a response from the Driver to the Sequence

- Sequencer can also arbitrate between multiple sequences and send a chosen transaction to the Driver

- Provides the following methods:

- send\_request (),

- get\_response ()

## **Driver**

#### **UVM TB Architecture: Driver**

- A UVM driver is responsible for decoding a transaction obtained from the

Sequencer

- It is responsible for driving the DUT interface signals

- It understands the pin level protocol and the <u>timing</u> relationships

- Driver receives the stimulus from **Sequence** via **Sequencer** and drives on interface signals.

## **UVM TB Architecture: Driver (2)**

1. Driver is written by extending the <a href="https://www.driver">uvm\_driver</a>,

```

class sync_fifo_driver extends uvm_driver #(sync_fifo_seq_item);

`uvm_component_utils(sync_fifo_driver)

// Constructor

function new (string name, uvm_component parent);

super.new(name, parent);

endfunction : new

endclass : mem_driver

```

## **UVM TB Architecture: Driver (3)**

2. Declare the virtual interface,

```

// Virtual Interface

virtual sync_fifo_if vif;

```

## **UVM TB Architecture: Driver (4)**

3. Get the interface handle using get config\_db,

```

if(!uvm_config_db # (virtual sync_fifo_if)::get(this, "", "vif", vif))

`uvm_fatal ("NO_VIF", {"virtual interface must be set for:", get_full_name(),".vif"});

```

## **UVM TB Architecture: Driver (5)**

4. Adding the get config\_db in the build\_phase,

```

function void build_phase(uvm_phase phase);

super.build_phase(phase);

if(!uvm_config_db#(virtual sync_fifo_if)::get(this, "", "vif", vif"))

`uvm_fatal("NO_VIF",{"virtual interface must be set for:", get_full_name(),".vif"});

endfunction: build_phase

```

## **UVM TB Architecture: Driver (6)**

5. Add driving logic, get the seq\_item and drive to DUT signals,

```

// run phase

virtual task run_phase(uvm_phase phase);

forever begin

seq_item_port.get_next_item(req);

//...

//.. driving logic ..here

//...

seq_item_port.item_done();

end

endtask : run_phase

```

## **Monitor**

#### **UVM TB Architecture: Monitor**

- Monitor's responsibility is to observe communication on the DUT interface

- A Monitor can include a protocol checker that can immediately find any pin level violations of the communication protocol

- Monitor samples the DUT signals through the virtual interface and converts the signal level activity to the transaction level.

- UVM Monitor is responsible for creating a transaction based on the activity on the interface

- This transaction is consumed by various testbench components for checking and <u>functional coverage</u>

- Monitor communicates with other testbench components using UVM Analysis ports

## **UVM TB Architecture: Monitor (2)**

1. The **Monitor** is written by extending the **uvm\_monitor**,

```

class sync_fifo_monitor extends uvm_monitor;

`uvm_component_utils(sync_fifo_monitor)

// new - constructor

function new (string name, uvm_component parent);

super.new(name, parent);

endfunction : new

endclass : sync_fifo_monitor

```

## **UVM TB Architecture: Monitor (3)**

2. Declare virtual interface,

```

// Virtual Interface virtual sync_fifo_if vif;

```

#### **UVM TB Architecture: Monitor (4)**

3. Connect interface to Virtual interface by using get method,

```

function void build_phase(uvm_phase phase);

super.build_phase(phase);

if(!uvm_config_db#(virtual sync_fifo_if)::get(this, "", "vif", vif))

`uvm_fatal("NOVIF",{"virtual interface must be set for: ", get_full_name(),".vif"});

endfunction: build_phase

```

## **UVM TB Architecture: Monitor (5)**

4. Declare Analysis port,

uvm\_analysis\_port #(sync\_fifo\_seq\_item) item\_collected\_port;

### **UVM TB Architecture: Monitor (6)**

5. Declare seq\_item handle, Used as a place holder for sampled signal activity,

sync\_fifo\_seq\_item trans\_collected;

## **UVM TB Architecture: Monitor (7)**

#### 6. Add Sampling logic in run\_phase,

- sample the interface signal and assign to trans\_collected handle

- sampling logic is placed in the forever loop

```

// run phase

virtual task run phase(uvm phase phase);

forever begin

//sampling logic

@(posedge vif.MONITOR.clk);

wait(vif.monitor_cb.wr_en | | vif.monitor_cb.rd_en);

trans collected.full = vif.monitor cb.full;

trans_collected.empty = vif.monitor_cb.empty;

if(vif.monitor_cb.wr_en) begin

trans collected.wr en = vif.monitor cb.wr en;

trans_collected.wdata = vif.monitor_cb.wdata;

trans_collected.rd_en = 0;

@(posedge vif.MONITOR.clk);

end

if(vif.monitor_cb.rd_en) begin

trans_collected.rd_en = vif.monitor_cb.rd_en;

trans_collected.wr_en = 0;

@(posedge vif.MONITOR.clk);

@(posedge vif.MONITOR.clk);

trans collected.rdata = vif.monitor cb.rdata;

end

end

endtask: run phase

```

### **UVM TB Architecture: Monitor (8)**

7. After sampling, by using the write method send the sampled transaction packet to the Scoreboard,

item\_collected\_port.write(trans\_collected);

# **Agent**

#### **UVM TB Architecture: Agent**

- An Agent is a <u>container class</u> contains a **Driver**, a **Sequencer**, and a **Monitor**.

- UVM Agent is responsible for connecting the sequencer, driver and the monitor

- It provides analysis ports for the monitor to send transactions to the scoreboard and coverage

- It provides the ability to disable the sequencer and driver; this will be useful when an actual DUT is connected

## **Scoreboard**

#### **UVM TB Architecture: Scoreboard**

- Scoreboard receives the transaction from the Monitor and compares it with the reference values.

- Scoreboard is one of the trickiest and most important verification components

- Scoreboard is an independent implementation of specification

- It takes in transactions from various monitors in the design, applies the inputs to the independent model and generates an expected output

- It then compares the actual and the expected outputs

- A typical **Scoreboard** is a queue implementation of the modeled outputs resulting in a pop of the latest result when the actual **DUT** output is available

- A Scoreboard also has to ensure that the timing of the inputs and outputs is well managed to avoid false fails

## **Environment**

#### **UVM TB Architecture: Environment**

- The Environment is the container class,

- It contains one or more Agents, as well as other components such as the Scoreboard, top-level Monitor, and checker.

- It means that

- It instantiates and connects:

- all the Agents

- all the Scoreboards

- all the functional coverage models

- And thus

- The **Environment** is responsible for managing various components in the testbench

#### **Test**

#### **UVM TB Architecture: Test**

- The **Test** defines the test scenario for the testbench.

- uvm\_test is responsible for

- creating the **Environment**

- controlling the type of test we want to run

- providing configuration information to all the components through the

Environment

## **Thank You**