### **Functional Verification**

Tuan Nguyen-viet

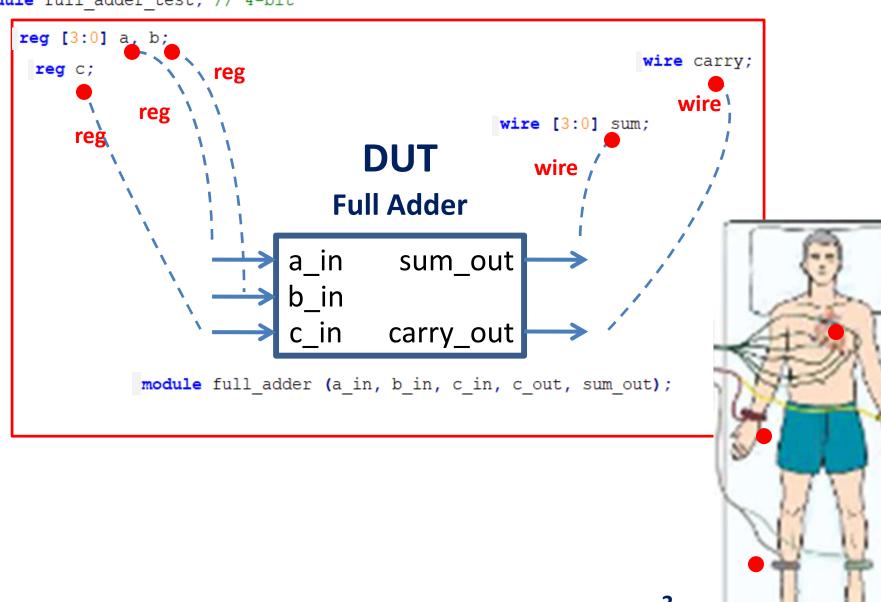

# **DUT** (full\_adder)

```

module full_adder (a_in, b_in, c_in, c_out, sum_out);

input [3:0] a_in, b_in;

input c_in;

output carry_out;

output [3:0] sum_out;

reg carry_out;

reg [3:0] sum_out;

always @ (a_in or b_in or c_in)

begin

{carry_out, sum_out} = a_in + b_in + c_in;

end

endmodule

```

### **Blank/Empty**

### **Test Bench**

```

module full adder test; // 4-bit

```

```

`timescale 1 ns/10 ps

module full adder test; // 4-bit

reg [3:0] a, b;

reg c;

wire [3:0] sum;

wire carry;

Connected

☐full adder dut (

.a in(a),

.b in(b),

.c in(c),

.carry out (carry) ,

.sum out (sum)

initial

begin

a = 4'b00000;

b = 4'b00000;

c = 1'b0;

#50;

a = 4'b0101;

b = 4'b1010;

// => sum=1111, carry=0

#50;

a = 4'b1111;

b = 4'b0001;

// => sum=0000, carry=1

#50;

a = 4'b00000;

b = 4'b11111;

c = 1'b1;

// => sum=0000, carry=1

#50:

a = 4'b0110;

b = 4'b0001;

// => sum=1000, carry=0

end

endmodule

```

### Test Bench (full\_adder\_test)

### **Blank/Empty**

# Test Bench (full\_adder\_tb)

```

`timescale 1 ns/10 ps

module full adder tb;

reg [3:0] a;

reg [3:0] b;

reg c;

wire [3:0] sum;

wire carry;

Connected

integer i;

☐full adder dut (

.a in(a),

.b in(b),

.c in(c),

.carry out (carry),

.sum out (sum)

);

initial

begin

a \le 0;

b <= 0;

c \ll 0;

$monitor ("a=0x%0h b=0x%0h c=0x%0h carry=0x%0h sum=0x%0h",

for (i=0; i < 5; i=i+1) begin

#10 a <= $random;

b <= $random;

c <= $random;

end

endmodule

```

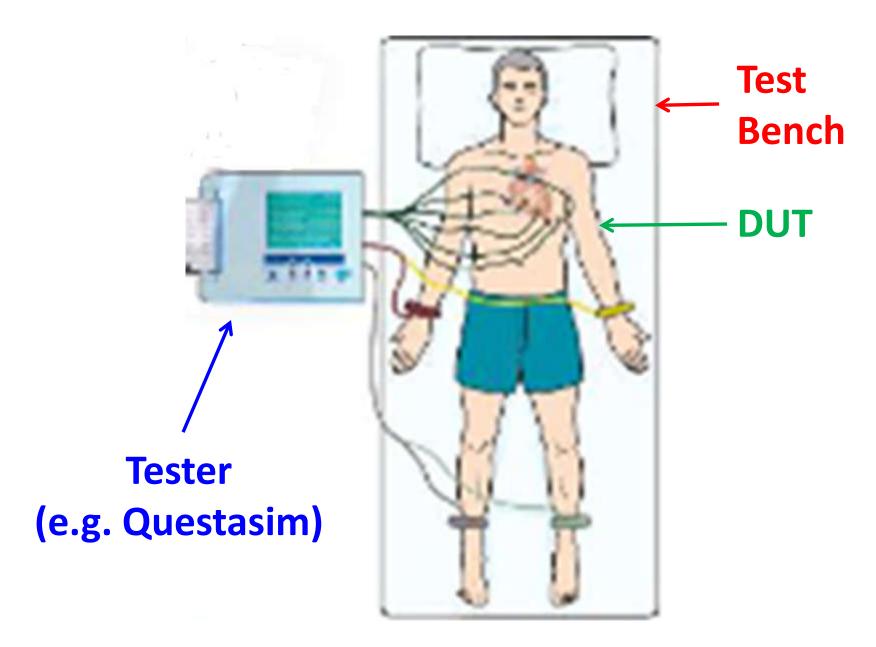

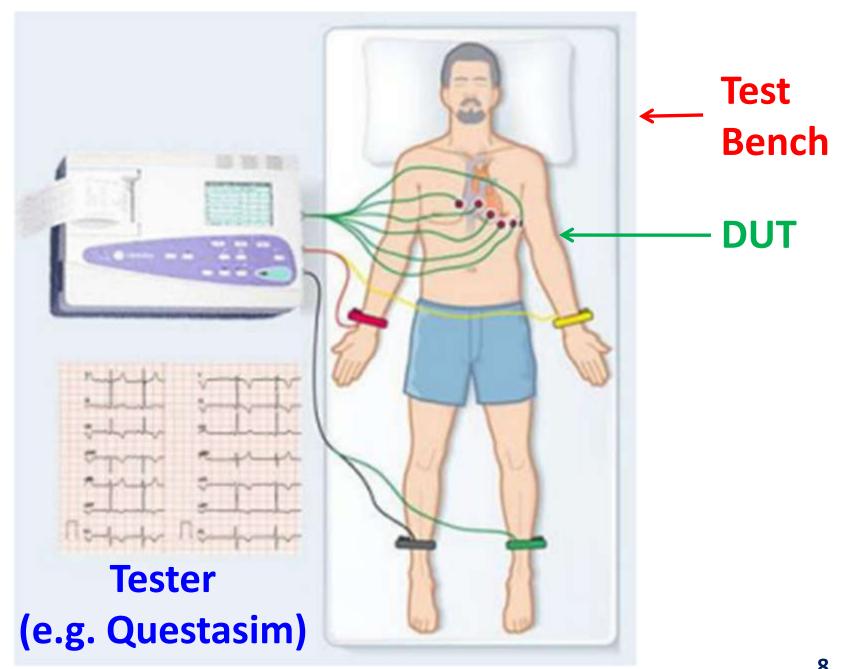

# Modelsim/Questasim (with PC)

```

`timescale 1 ns/10 ps

module full adder tb;

reg [3:0] a;

reg [3:0] b;

reg c;

wire [3:0] sum;

wire carry;

integer i;

□full adder dut (

.a in(a),

.b in(b),

.c in(c),

.carry out (carry) ,

.sum out(sum)

);

initial

begin

a \le 0;

b \le 0;

c \le 0;

$monitor ("a=0x%0h b=0x%0h c=0x%0h carry=0x%0h sum=0x%0h", a, b, c, carry, sum);

for (i=0; i < 5; i=i+1) begin

#10 a <= $random;

b <= $random;

c <= $random;

end

end

9

endmodule

```

#### QuestaSim

- QuestaSim is a functional verification simulator of Mentor Graphics,

- developed as an integrated platform under Questa Advanced

Simulator software,

- which is the core <u>simulation</u> and <u>debugging</u> engine.

- powered by ModelSim tool,

- which both are the software products belonging to the same company.

- QuestaSim offers

- higher capacity and supports larger FPGA and SoC,

- where ModelSim supports smaller designs.

### QuestaSim (2)

- Because of its **verification** supportive nature, QuestaSim

- is compatible with a large array of languages containing

- Verilog HDL,

- SystemVerilog

- and VHDL;

- and offers support for SystemVerilog based **UVM libraries** in hardware description and verification.

- QuestaSim was used for running the complete UVM testbench

- in order to observe the verification results.

### QuestaSim (3)

- One of the main differences between QuestaSim and Modelsim (besides performance/capacity) is that

- QuestaSim is the simulation engine for the Questa Platform which includes integration of

- Verification Management,

- Formal based technologies,

- Questa Verification IP,

- Low Power Simulation and

- Accelerated Coverage Closure technologies.

- QuestaSim natively supports SystemVerilog for Testbench, UPF, UCIS, OVM/UVM.

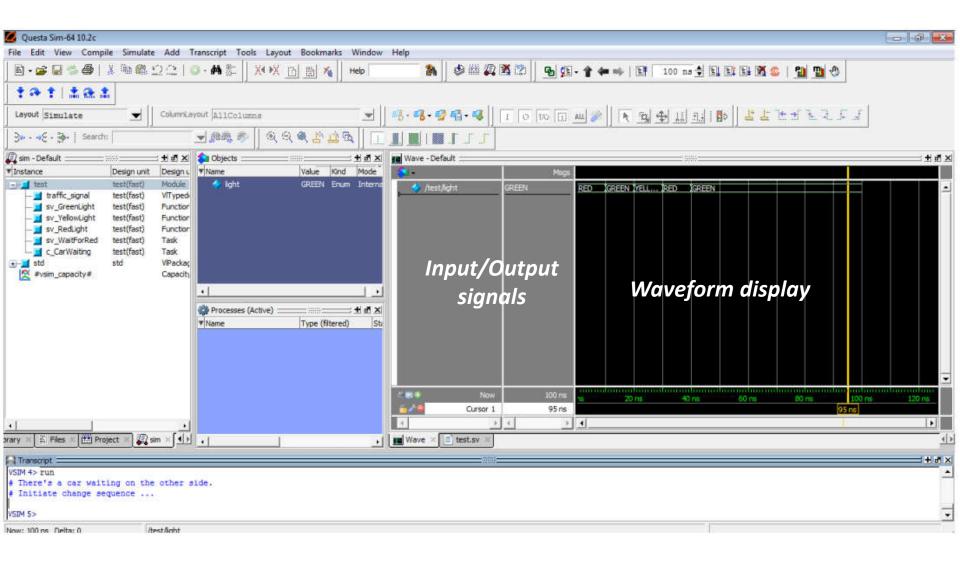

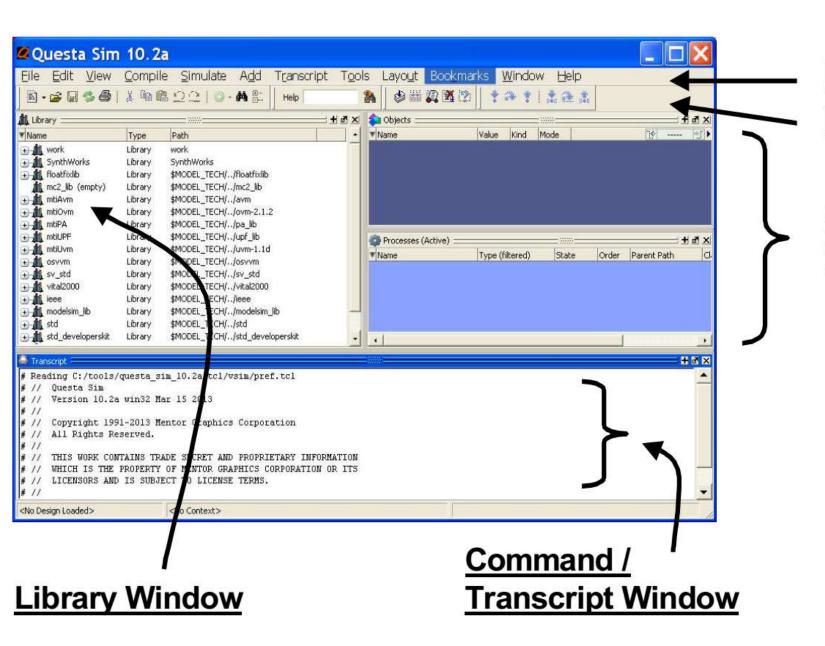

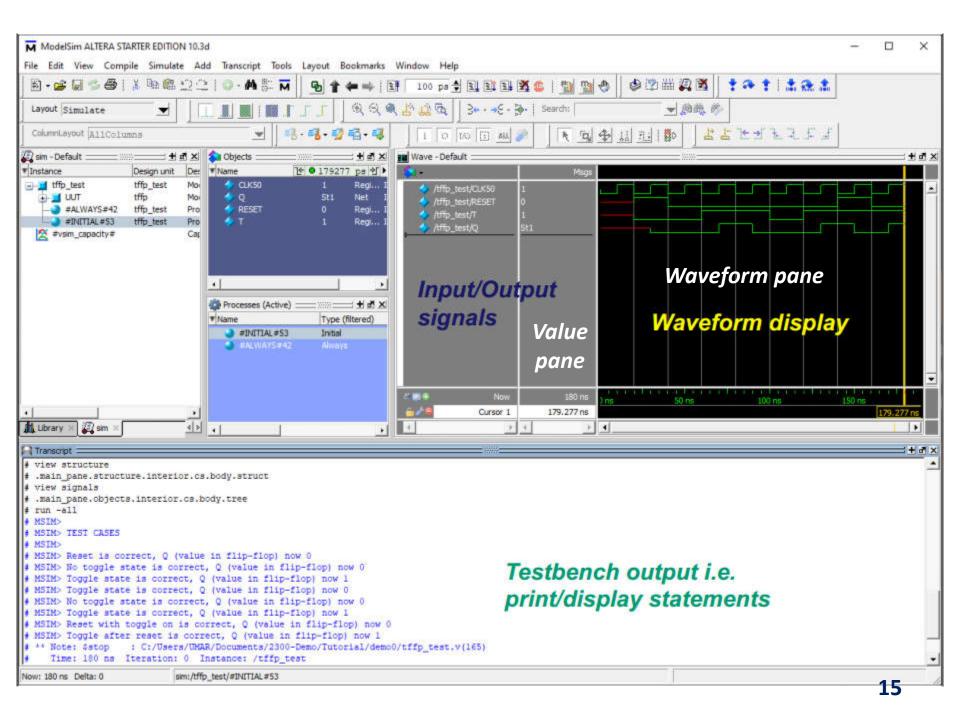

### A screenshot from QuestaSim simulation environment

Menu Buttons

Other Windows

| Buttons | Description*                                                                                                                                                                              | Command Line                                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Compile this file open the Compile Source File dialog; in a project, compile the file                                                                                                     | To compile:  vlog -work [working library] [filename.v] ex) vlog -work work tb_tutorial.v  To recompile:  vlog -work [working library] -refresh |

|         | Compile All compile all files in the open project                                                                                                                                         | Compile > Compile All                                                                                                                          |

|         | Simulate<br>load the selected design unit or simulation<br>configuration object                                                                                                           | <pre>vsim -c [working library].[file name] Ex) vsim -c work.tb_tutorial</pre>                                                                  |

|         | Restart reload the design elements and reset the simulation time to zero, with the option of using current formatting, breakpoints, WLF file, virtual definitions, and assertion settings | restart -f                                                                                                                                     |

| E.      | Run run the current simulation for the specified run length                                                                                                                               | run                                                                                                                                            |

|         | Open Wave Viewer                                                                                                                                                                          | Window > Wave                                                                                                                                  |

| [J      | Zoom Mode<br>set mouse to Zoom Mode – drag left mouse<br>button to zoom, click middle mouse button<br>to select                                                                           | N/A                                                                                                                                            |

| £.      | Insert Cursor add a cursor to the waveform pane                                                                                                                                           | Insert > Cursor                                                                                                                                |

# **Thank You**