# Design of mixed signal SOCs

#### Lukas Pertoll, Weissteiner Hannes

Graz, 09.12.2020

#### Content

- Introduction

- Where is it used?

- Challenges

- Problems & Solutions

- Mixed signals and FPGAs

## What is a mixed signal SOC?

- SOC with analog and digital signals

- Measure analog signals and process right away

- Create analog signals after processing digital input

- Combination of both

- Examples:

- Zybo

- MSP430

- Radio Modules

- •

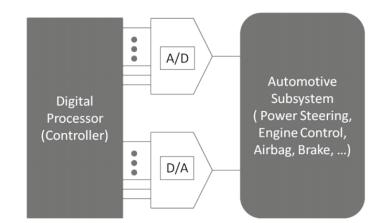

Example for a mixed-signal automotive design

Graz, 09.12.2020

#### Where is it used?

- Smart sensors

- IoT-Devices

- Small robots

- Software-defined Radio

# Challenges

- High level of abstraction for IP and reuse based methodologies.

- Low level analysis for physical effects on small process nodes.

- Analog and digital IO, as well as RF integrated into one chip.

#### Problems

- 1. Simulation

- Digital simulation does not support analog values

- Analog circuit simulation too slow

- 2. Verification

- 3. Creating the chip

- Electric Interference

- RF behavior

# Simulation: Real Number Models

- Digital simulation with real numbers

- Best used for high-frequency signals

- Low-frequency and DC simulation in SPICE

- Good simulation performance

- Example:

- SystemVerilog (IEEE 1800-2012, SV-RNM)

# Simulation: Verilog-AMS

- Analog behavioural modelling

- Works with standard digital test environments

- Continuous time analog simulation

- Analog and digital solvers

- Alternatives:

- VHDL-AMS

- SystemC-AMS

## Simulation: Verilog-AMS Examples

- "electrical" adds voltage and current to pin-

- Contribution statement <+ assigns values continuously

- Instantiate modules between nodes and set values

| L1 (i1 0) inductor l=1uH<br>L2 (i2 0) inductor l=2uH r=1 | <pre>module inductor(p, n);<br/>inout p, n;<br/>electrical p, n;<br/>parameter real l=1 from [0:in<br/>parameter real r=0 from [0:in<br/>analog begin<br/>  V(p,n) &lt;+ l*ddt(I(p,n)) +<br/>end<br/>endmodule</pre> | nf);                        |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|                                                          | Graz, 09.12.2020                                                                                                                                                                                                     | Design of mixed signal SOCs |

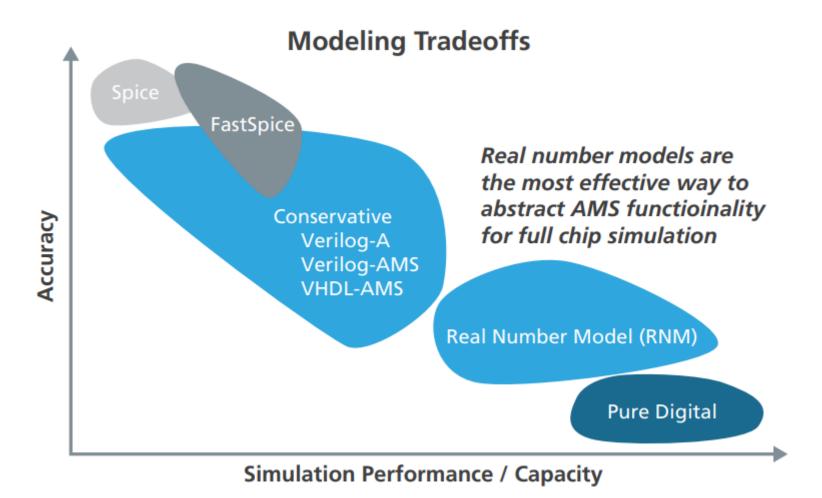

#### Comparison of simulation methods

Graz, 09.12.2020

**Design of mixed signal SOCs**

#### Verification

- Digital verification:

- Universal Verification Methodology (UVM)

- Metric-driven Verification (MDV, Coverage driven)

- Mixed-Signal Verification:

- MS-MDV

- UVM with RNM

- Allows assertions with real numbers

- Requires well-tested individual blocks

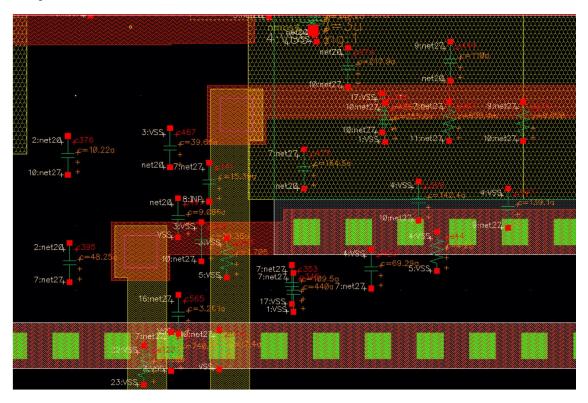

#### Parasitic extraction

- Large parasitic effects for small processes

- Post layout simulation

Graz, 09.12.2020

**Design of mixed signal SOCs**

#### Verification

- Time to market, first time right

- Simulation performance

- Shrinking process nodes => physical effects

- Interaction between analog and digital

- Foundry verified golden models and simulators

- Tight link to parasitic extraction tool

- Support for multiple levels of circuit abstraction

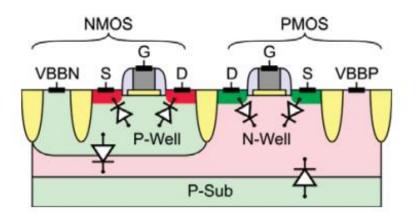

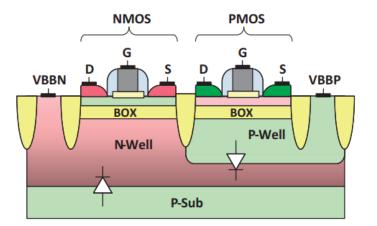

#### Silicon on insulator

Traditional CMOS

Silicon on insulator

- Parasitic diodes connected to the substrate

- Substrate coupling

#### Silicon on insulator

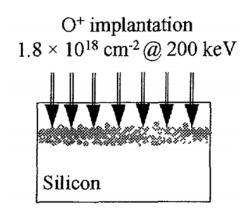

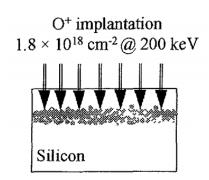

SIMOX: Separation by Implantation of Oxygen

- Implant O<sup>+</sup> Ions, energy and fluence determines range and thickness

- Continuously anneal damaged silicon @ 600-1400°C

#### **TU** Graz

#### Silicon on insulator

SIMOX: Seperation by Implantation of Oxygen

- Implant O<sup>+</sup> Ions, energy and fluence

- determines range and thickness

- Continuously anneal damaged silicon @ 600-1400°C

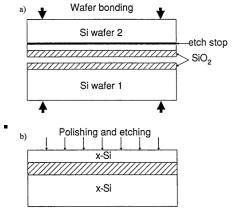

**BESOI: Bond and Etch-Back SOI**

- Bond to separate wafers

- Create etch block by implanting B or Ge.

#### **Design of mixed signal SOCs**

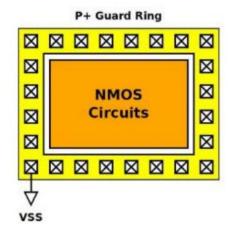

# SOI vs Guard rings

Guard ring: Ring in silicon and metal layers

- Reduce substrate coupling significantly

- Increased area

- Easy

#### Silicon on Insulator

- Reduced substrate coupling

- Reduced gate and parasitic capacity

- No additional area

- More expensive

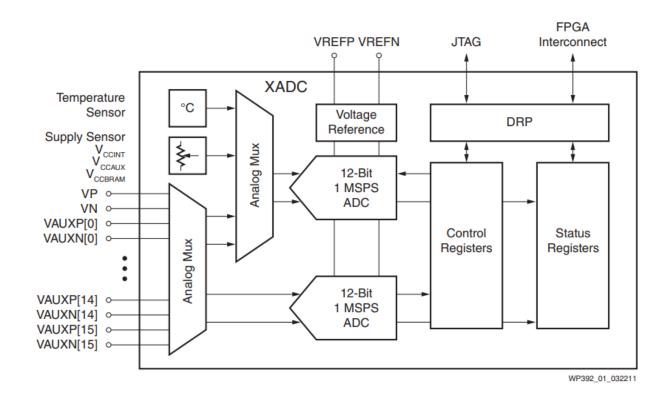

## Mixed signals and FPGAs

- FPGAs support only digital signals

- Digital input from ADC, analog output by DAC

- Placed on the chip or provided by processor

- System is mixed-signal, FPGA is not

- Prototype FPAAs, nothing useful yet

#### Zynq-7000

#### Internal dual 12 bit ADC with 1Msps

#### ChipScope Pro

#### View analog Inputs without design

|                                     | XADC Console - Devi | ce:0                                | ಕರ                                                                              |

|-------------------------------------|---------------------|-------------------------------------|---------------------------------------------------------------------------------|

| JTAG Chain                          | Sensor              | Value                               | History                                                                         |

| P DEV:0 MyDevice0 (XC7K325T)        |                     |                                     |                                                                                 |

| XADC Console                        |                     |                                     | .5 C 32.0 C-<br>.0 C 31.0 C-                                                    |

|                                     |                     |                                     | .s c 30.0 C-                                                                    |

|                                     |                     | Sampled Max NA                      | 29.0 C - V V V V V V V V V V                                                    |

|                                     | Die Temperature     | Sampled Min NA                      | 28.0 C -                                                                        |

|                                     |                     | Window Avg NA                       | 27.0 C -                                                                        |

|                                     |                     | Window Max NA                       | 26.0 C -                                                                        |

|                                     |                     | Window Min NA                       | 25.0 C -                                                                        |

|                                     |                     | THINGS WITH THY                     | 24.0 C - 18:13:01 18:13:17 18:13:33 18:13:49 18:14:05 18:14:21 18:14:37 18:14:  |

| Sensors: DEV: 0 UNIT: XADC          |                     | Present 0.99                        | 95 V 1.000 V -                                                                  |

| <ul> <li>On-Chip Sensors</li> </ul> |                     |                                     | 77 ¥ 0.999 ¥ -                                                                  |

|                                     |                     |                                     | 93 V 0.998 V -                                                                  |

|                                     | DOODT O             | Sampled Max NA                      |                                                                                 |

|                                     | VCCINT Supply       | Sampled Min NA                      | 01993 (                                                                         |

|                                     |                     | Window Avg NA                       | 0.994 V -                                                                       |

|                                     |                     | Window Max NA                       | 0.992 V - 0.991 V -                                                             |

|                                     |                     | Window Min NA                       | 0.900 7 -                                                                       |

|                                     |                     |                                     | 18:13:01 18:13:17 18:13:33 18:13:49 18:14:05 18:14:21 18:14:37 18:14:           |

|                                     |                     | Present 1.79                        | 91 V 1.800 V-                                                                   |

|                                     |                     | Device Max 1.79                     |                                                                                 |

|                                     |                     | Device Min 1.78                     |                                                                                 |

|                                     | VCCAUX Supply       | Sampled Max NA                      |                                                                                 |

|                                     | recuta o 411,       | Sampled Min NA                      |                                                                                 |

|                                     |                     | Window Avg NA                       | 1.785 V -                                                                       |

|                                     |                     | Window Max NA                       | 1.783 Y -                                                                       |

|                                     |                     | Window Min NA                       | 1.280 X -                                                                       |

|                                     |                     |                                     |                                                                                 |

|                                     |                     | Present 0.99                        |                                                                                 |

|                                     |                     | Device Max 1.00                     |                                                                                 |

|                                     |                     | Device Min 0.99                     | 96 V 1.005 V -<br>1.003 V -                                                     |

|                                     | VCCBRAM             | Sampled Max NA                      |                                                                                 |

|                                     |                     | Sampled Min NA                      | 0.998 7 -                                                                       |

|                                     |                     | Window Avg NA                       | 0.995 Y -                                                                       |

|                                     |                     | Window Max NA                       | 0.992 V -                                                                       |

|                                     |                     | Addisonal associations and a second |                                                                                 |

|                                     |                     | Window Min NA                       | 0.990 Y - 18:13:01 18:13:17 18:13:33 18:13:49 18:14:05 18:14:21 18:14:37 18:14: |

**Design of mixed signal SOCs**

- RF/Analog and Mixed-Signal Design Techniques in FD-SOI Technology by Andreia Cathelin, STMicroelectronics

- Xilinx Analog Mixed Signal Solutions by Anthony Collins, XILINX

- Reduction of Substrate Noise in Mixed-Signal Circuits by Erik Backenius, Linköping University

- What's needed for mixed-signal verification by Bijan Kiani, EETimes

- Applying Mixed-Signal Verification Best Practices to Mixed-Signal ICs for Automotive Applications, Cadence Design Systems

- Parasitic Extraction, Post-layout and Back annotating in Circuit Design by Alberto L., Mis Circuitos

- Complete DFM Model for High-Performance Computing SoCs with Guard Ring and Dummy Fill Effect by Chun-Chen Liu, Oscar Lau, Jason Y. Du University of California

#### Sources

- Solutions for Mixed-Signal SoC Verification by Kishore Karnane and Sathishkumar Balasubramanian, Cadence Design Systems

- Metric Driven Verification, Aldec

| Graz, 09.12.2020 | Design of mixed signal SOCs |

|------------------|-----------------------------|

|                  |                             |