# Questasim Tutorial (GUI/Windows)

**Continued**

REF: ModelSim® Tutorial

Software Version 10.4c

# Part 1: Reqs and Specs

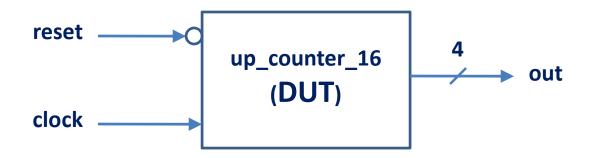

#### **Design** of 4-bit Up Counter

```

module up counter 16

2

out, // Output of the counter

3

clock, // clock Input

4

reset // reset Input

5

);

6

input clock, reset;

output [3:0] out;

reg [3:0] out; // internal variable

10

11

12

always @ (posedge clock)

13

if (! reset) out <= 4'b0 ;</pre>

14

else

out <= out + 1;

15

16

endmodule

```

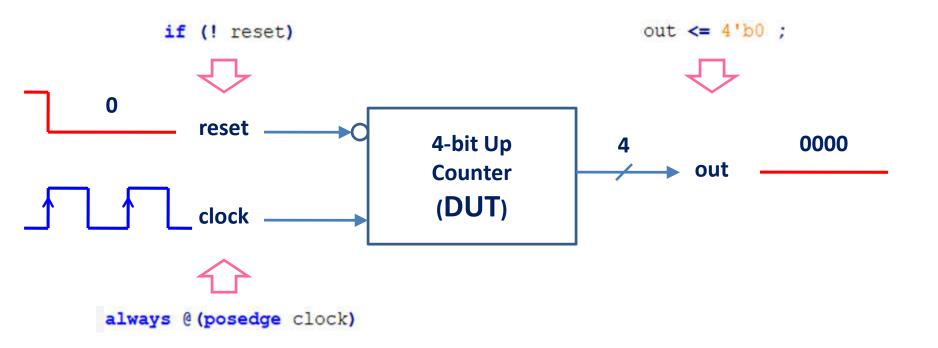

# **Reqs/Specs** for the Design

```

always @ (posedge clock)

if (! reset) out <= 4'b0 ;</pre>

```

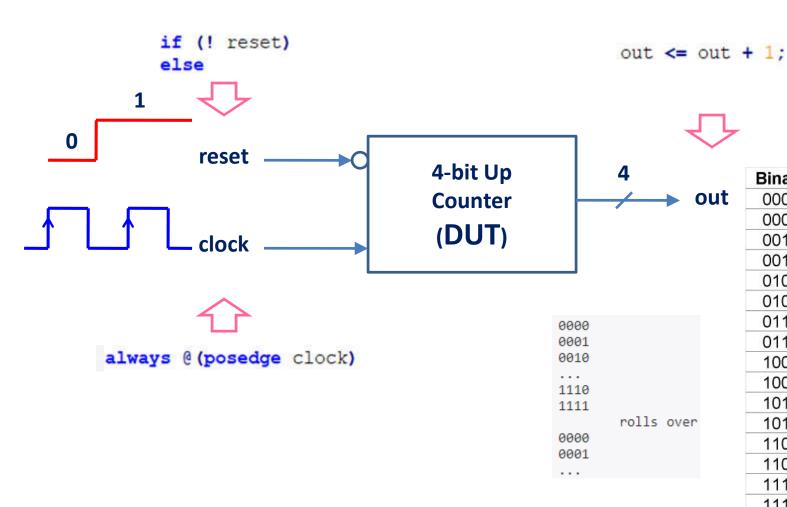

# Reqs/Specs for the Design (2)

```

always @(posedge clock)

if (! reset) out <= 4'b0 ;</pre>

```

| Di     | D!!     |     |

|--------|---------|-----|

| Binary | Decimal | Hex |

| 0000   | 0       | 0   |

| 0001   | 1       | 1   |

| 0010   | 2       | 2   |

| 0011   | 3       | 3   |

| 0100   | 4       | 4   |

| 0101   | 5       | 5   |

| 0110   | 6       | 6   |

| 0111   | 7       | 7   |

| 1000   | 8       | 8   |

| 1001   | 9       | 9   |

| 1010   | 10      | Α   |

| 1011   | 11      | В   |

| 1100   | 12      | С   |

| 1101   | 13      | D   |

| 1110   | 14      | E   |

| 1111   | 15      | F   |

# 4-bit Up Counter (3)

# **Part 2: Using Testbench File for Stimulus**

#### **Testbench File for Stimulus**

```

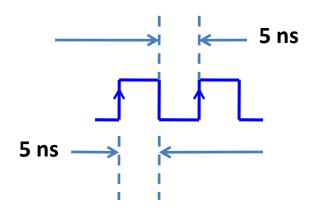

always #5 clk = ~clk;

```

```

// 1. Initialize testbench variables to 0

clk <= 0;

rstn <= 0;

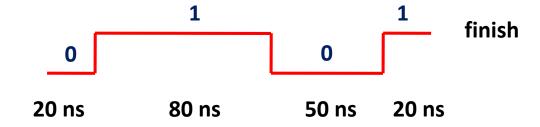

// 2. Drive rest of the stimulus

#20 rstn <= 1;

#80 rstn <= 0;

#50 rstn <= 1;

// 3. Finish the stimulus after 200ns

#20 $finish;</pre>

```

```

timescale 1 ns/10 ps

module up counter 16 tb;

reg clk;

reg rstn;

wire [3:0] out;

// Instantiate counter design

□up counter 16 dut (

.clock (clk),

.reset (rstn),

.out (out)

);

always #5 clk = ~clk;

initial

begin

// 1. Initialize testbench variables to 0

clk \le 0;

rstn <= 0;

// 2. Drive rest of the stimulus

#20 rstn <= 1;

#80 rstn <= 0;

#50 rstn <= 1;

// 3. Finish the stimulus after 200ns

#20 $finish;

end

endmodule

```

# Part 3: Using 'Add to List' for Stimulus

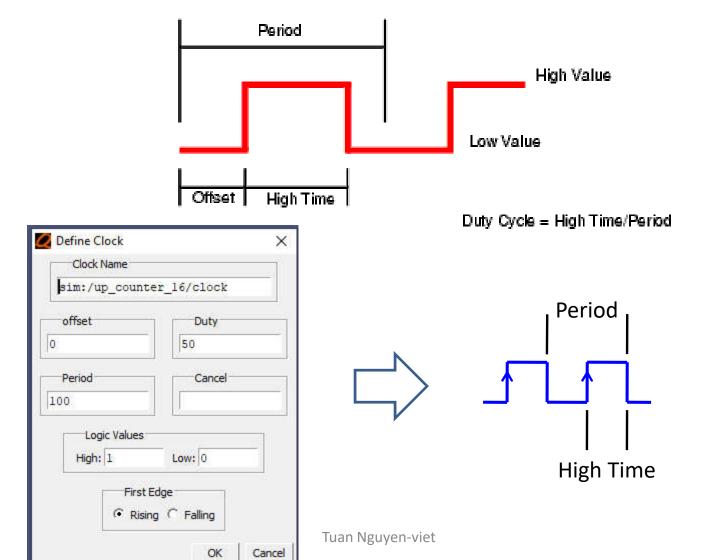

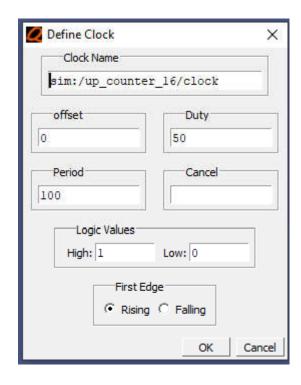

#### **Defining Clock**

- For clock signals starting on the rising edge,

- the definition for Period, Offset, and Duty Cycle is as follows:

# **Apply Clock**

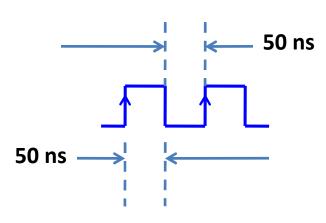

# Force Reset to '1' / '0' / '1'

# Part 4: Using .DO file for Stimulus

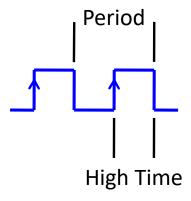

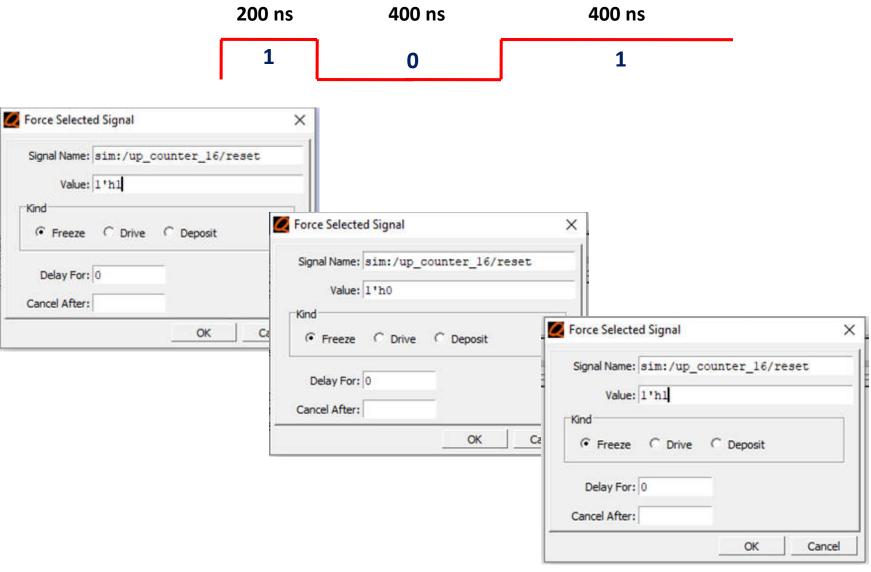

#### .DO file: Apply Clock

#### force -freeze clock 0 0, 1 {5 ns} -r 10

0: value at time 0 ns

1: value applied at 5 ns

-r : to repeat at required interval

10: the number of ns of the repeat interval

# **Apply Reset signal**

### .DO file (sim.do)

```

vsim up_counter_16

add wave out

add wave clock

add wave reset

force -freeze clock 0 0, 1 {50 ns} -r 100

force reset 1

run 100

force reset 0

run 300

force reset 1

run 400

force reset 0

run 200

```

### **Thank You**